# RAGE MOBILITY M6/D6/P6

### Technical Reference Manual

#### P/N: DSG-216M6-00-03

© 2000 ATI Technologies

#### **CONFIDENTIAL MATERIAL**

All information contained in this manual is confidential material of ATI Technologies Inc. Unauthorized use or disclosure of the information contained herein is prohibited. You may be held responsible for any loss or damage suffered by ATI for your unauthorized disclosure hereof, in whole or in part. Please exercise the following precautions:

- Store all hard copies in a secure place when not in use.

- Save all electronic copies on password protected systems.

- Do not reproduce or distribute any portions of this manual in paper or electronic form (except as permitted by ATI).

- Do not post this manual on any LAN or WAN (except as permitted by ATI).

Your protection of the information contained herein may be subject to periodic audit by ATI. This manual is subject to possible recall by ATI.

The information contained in this manual has been carefully checked and is believed to be entirely reliable. No responsibility is assumed for inaccuracies. ATI reserves the right to make changes at any time to improve design and supply the best product possible.

ATI, mach64, 3D RAGE, and RAGE Mobility are trademarks of ATI Technologies Inc. All other trademarks and product names are properties of their respective owners.

## Table of Contents

| 1 In                                                                                    | troduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                    |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 1.1                                                                                     | About This Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .10                                                                                                   |

| 1.2                                                                                     | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 1.3                                                                                     | Supported Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 2 G                                                                                     | raphics Subsystem Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11                                                                                                    |

| 2.1                                                                                     | Considerations for the Layout of the Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

| 2.2                                                                                     | Subsystem Grounding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |

| 2.3                                                                                     | Power Supply Decoupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 2.4                                                                                     | Optionally Unused Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 3 PC                                                                                    | ower and Ground Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24                                                                                                    |

| 3.1                                                                                     | Estimated Current and Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 3.2                                                                                     | Layout Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 3.3                                                                                     | VIAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 3.4                                                                                     | Decoupling Capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 3.4<br>3.5                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

|                                                                                         | Split VDDC Power Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 3.6                                                                                     | Separate Analog and PLL Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 3.7                                                                                     | Signal Routing Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

| 3.8                                                                                     | Power sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .29                                                                                                   |

|                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

| 1 1                                                                                     | GP Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22                                                                                                    |

|                                                                                         | GP Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |

| 4.1                                                                                     | Applicable Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .32                                                                                                   |

| 4.1<br>4.2                                                                              | Applicable Specifications<br>Physical Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .32<br>.32                                                                                            |

| 4.1<br>4.2<br>4.3                                                                       | Applicable Specifications<br>Physical Connections<br>Unused Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 32<br>. 32<br>. 33                                                                                  |

| 4.1<br>4.2<br>4.3<br>4.4                                                                | Applicable Specifications<br>Physical Connections<br>Unused Signals<br>Signal Levels and Electrical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .32<br>.32<br>.33<br>.33                                                                              |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4                                                         | Applicable Specifications<br>Physical Connections<br>Unused Signals<br>Signal Levels and Electrical Requirements<br>1 Signal Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .32<br>.32<br>.33<br>.33<br>.33                                                                       |

| 4.1<br>4.2<br>4.3<br>4.4                                                                | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         .1       Signal Levels         .2       VDDP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .32<br>.32<br>.33<br>.33<br>33<br>33                                                                  |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4                                                  | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         .1       Signal Levels         .2       VDDP         .3       VDDP Decoupling         .4       STP_AGPb and AGP Interface Power Management Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .32<br>.33<br>.33<br>33<br>33<br>34<br>34                                                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4                                    | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDDP         3       VDDP Decoupling         .4       STP_AGPb and AGP Interface Power Management Output         .5       AGP Voltage Reference (AGPREF)                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .32<br>.33<br>.33<br>33<br>33<br>34<br>34<br>35                                                       |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4                             | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDDP         3       VDDP Decoupling         4       STP_AGPb and AGP Interface Power Management Output         5       AGP Voltage Reference (AGPREF)         6       AGPTEST                                                                                                                                                                                                                                                                                                                                                                                                                              | .32<br>.33<br>.33<br>33<br>33<br>34<br>34<br>35<br>36                                                 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5                             | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDDP         3       VDDP Decoupling         4       STP_AGPb and AGP Interface Power Management Output         5       AGP Voltage Reference (AGPREF)         6       AGPTEST         Layout and Routing Considerations                                                                                                                                                                                                                                                                                                                                                                                    | .32<br>.33<br>.33<br>33<br>33<br>34<br>34<br>35<br>36<br>36                                           |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5                      | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         .1       Signal Levels         .2       VDDP         .3       VDDP Decoupling         .4       STP_AGPb and AGP Interface Power Management Output         .5       AGP Voltage Reference (AGPREF)         .6       AGPTEST         Layout and Routing Considerations         .1       General Guidelines                                                                                                                                                                                                                                                                                                                                          | .32<br>.33<br>.33<br>.33<br>.33<br>.34<br>.34<br>.35<br>.36<br>.36<br>.36                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5               | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         .1       Signal Levels         .2       VDDP         .3       VDDP Decoupling         .4       STP_AGPb and AGP Interface Power Management Output         .5       AGP Voltage Reference (AGPREF)         .6       AGPTEST         Layout and Routing Considerations         .1       General Guidelines         .2       AGP Address/Data and SideBand Strobes                                                                                                                                                                                                                                                                                   | .32<br>.33<br>.33<br>.33<br>.33<br>.34<br>.34<br>.34<br>.35<br>.36<br>.36<br>.36<br>.37               |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.5<br>4.5 | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         .1       Signal Levels         .2       VDDP         .3       VDDP Decoupling         .4       STP_AGPb and AGP Interface Power Management Output         .5       AGP Voltage Reference (AGPREF)         .6       AGPTEST         Layout and Routing Considerations         .1       General Guidelines         .2       AGP Address/Data and SideBand Strobes         .3       Trace Length                                                                                                                                                                                                                                                     | .32<br>.33<br>.33<br>33<br>33<br>34<br>34<br>35<br>36<br>36<br>36<br>37<br>37                         |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.5<br>4.5 | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDDP         3       VDDP Decoupling         4       STP_AGPb and AGP Interface Power Management Output         5       AGP Voltage Reference (AGPREF)         .6       AGPTEST         Layout and Routing Considerations         .1       General Guidelines         .2       AGP Address/Data and SideBand Strobes         .3       Trace Length         .4       Substrate Trace Length Report (AGP Section)                                                                                                                                                                                             | .32<br>.33<br>.33<br>.33<br>.33<br>.34<br>.34<br>.34<br>.35<br>.36<br>.36<br>.36<br>.37<br>.37<br>.37 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.5<br>4.5 | Applicable Specifications         Physical Connections         Unused Signals.         Signal Levels and Electrical Requirements.         1       Signal Levels         2       VDDP         3       VDDP Decoupling.         4       STP_AGPb and AGP Interface Power Management Output.         5       AGP Voltage Reference (AGPREF)         .6       AGPTEST.         Layout and Routing Considerations.         .1       General Guidelines         .2       AGP Address/Data and SideBand Strobes.         .3       Trace Length         .4       Substrate Trace Length Report (AGP Section)         Guarding and Trace Pitch.                                                                                                                                                    | .32<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33                                    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.5<br>4.5 | Applicable Specifications         Physical Connections         Unused Signals.         Signal Levels and Electrical Requirements.         1       Signal Levels         2       VDDP         3       VDDP Decoupling.         4       STP_AGPb and AGP Interface Power Management Output.         5       AGP Voltage Reference (AGPREF)         6       AGPTEST.         Layout and Routing Considerations.         1       General Guidelines         2       AGP Address/Data and SideBand Strobes.         3       Trace Length         4       Substrate Trace Length Report (AGP Section)         Guarding and Trace Pitch.         1       Interface Control Signals.         2       RESET                                                                                        | .32<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33                                    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.5<br>4.5 | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDP         3       VDDP Decoupling         4       STP_AGPb and AGP Interface Power Management Output         5       AGP Voltage Reference (AGPREF)         6       AGPTEST         Layout and Routing Considerations         .1       General Guidelines         .2       AGP Address/Data and SideBand Strobes         .3       Trace Length         .4       Substrate Trace Length Report (AGP Section)         Guarding and Trace Pitch         .1       Interface Control Signals         .2       RESET         .3       PCICLK                                                                    | .32<br>.33<br>.33<br>33<br>33<br>33<br>33<br>33<br>                                                   |

| $\begin{array}{c} 4.1\\ 4.2\\ 4.3\\ 4.4\\ 4.4\\ 4.4\\ 4.4\\ 4.4\\ 4.5\\ 4.5\\ 4.5$      | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDP         3       VDP Decoupling         4       STP_AGPb and AGP Interface Power Management Output         5       AGP Voltage Reference (AGPREF)         6       AGPTEST         Layout and Routing Considerations         1       General Guidelines         2       AGP Address/Data and SideBand Strobes         3       Trace Length         4       Substrate Trace Length Report (AGP Section)         Guarding and Trace Pitch         1       Interface Control Signals         2       RESET         3       PCICLK         Interface Configuration / Straps                                   | .32<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33                                    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.5<br>4.5 | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDDP         3       VDDP Decoupling         4       STP_AGPb and AGP Interface Power Management Output         5       AGP Voltage Reference (AGPREF)         6       AGPTEST         Layout and Routing Considerations         1       General Guidelines         2       AGP Address/Data and SideBand Strobes         3       Trace Length         4       Substrate Trace Length Report (AGP Section)         Guarding and Trace Pitch         1       Interface Control Signals         2       RESET         3       PCICLK         Interface Configuration / Straps         1       External Straps | .32<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33                                    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.5 | Applicable Specifications         Physical Connections         Unused Signals         Signal Levels and Electrical Requirements         1       Signal Levels         2       VDP         3       VDP Decoupling         4       STP_AGPb and AGP Interface Power Management Output         5       AGP Voltage Reference (AGPREF)         6       AGPTEST         Layout and Routing Considerations         1       General Guidelines         2       AGP Address/Data and SideBand Strobes         3       Trace Length         4       Substrate Trace Length Report (AGP Section)         Guarding and Trace Pitch         1       Interface Control Signals         2       RESET         3       PCICLK         Interface Configuration / Straps         1       External Straps   | .32<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33<br>.33                                    |

RAGE MOBILITY M6 Graphics Subsystem Design Guide

Page 2

| 4.7.3 VGA Disable - GPIO[7]                                                                                                                                                                                       |                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7.4 ID Disable – GPIO[8]                                                                                                                                                                                        |                                                                                                                                                                            |

| 4.7.5 Bus-configuration Straps - GPIO[6:4]                                                                                                                                                                        |                                                                                                                                                                            |

| 4.7.6 AGP Skew Straps - GPI0[1] and GPI0[0]                                                                                                                                                                       |                                                                                                                                                                            |

| 4.7.7 X1CLK_Skew Straps - GPI0[3] and GPI0[2]<br>4.7.8 ROMIDCFG Straps - GPI0[13:11]                                                                                                                              |                                                                                                                                                                            |

| 4.1.8 KOMIDERG Straps - Grio(13.11]                                                                                                                                                                               |                                                                                                                                                                            |

| 5 PLL (Phase Lock Loop) Interface                                                                                                                                                                                 | 52                                                                                                                                                                         |

| 5.1 Physical Connections                                                                                                                                                                                          |                                                                                                                                                                            |

| 5.2 Clock Overview                                                                                                                                                                                                |                                                                                                                                                                            |

| 5.3 Engine and Memory Clocks                                                                                                                                                                                      |                                                                                                                                                                            |

| 5.3.1 Engine Clock - SCLK                                                                                                                                                                                         | 53                                                                                                                                                                         |

| 5.3.2 Memory Interface Clock - MCLK                                                                                                                                                                               |                                                                                                                                                                            |

| 5.4 Engine and Memory Clock Frequency                                                                                                                                                                             | 54                                                                                                                                                                         |

| 5.5 Reference Clock Source: Crystal versus Oscillator                                                                                                                                                             | 54                                                                                                                                                                         |

| 5.6 Reference Frequencies                                                                                                                                                                                         | 54                                                                                                                                                                         |

| 5.7 Reference Clock Connections                                                                                                                                                                                   |                                                                                                                                                                            |

| 5.7.1 Using RAGE MOBILITY M6 in Stand-alone Designs                                                                                                                                                               | 54                                                                                                                                                                         |

| 5.8 Oscillator Circuit                                                                                                                                                                                            |                                                                                                                                                                            |

| 5.9 Power and Grounding                                                                                                                                                                                           |                                                                                                                                                                            |

| 5.9.1 PVDD, MPVDD, LPVDD, TPVDD                                                                                                                                                                                   |                                                                                                                                                                            |

| 5.9.2 PVSS, MPVSS, LPVSS, TPVSS                                                                                                                                                                                   |                                                                                                                                                                            |

| 6 One shine Manageme                                                                                                                                                                                              |                                                                                                                                                                            |

|                                                                                                                                                                                                                   | <b>F7</b>                                                                                                                                                                  |

| 6 Graphics Memory                                                                                                                                                                                                 |                                                                                                                                                                            |

| 6.1 Överview                                                                                                                                                                                                      | 57                                                                                                                                                                         |

| 6.1 Overview<br>6.1.1 Support for SDR SDRAM Memory                                                                                                                                                                | 57<br>57                                                                                                                                                                   |

| 6.1 Overview<br>6.1.1 Support for SDR SDRAM Memory<br>6.1.2 Support for SDR SGRAM Memories                                                                                                                        |                                                                                                                                                                            |

| 6.1       Overview         6.1.1       Support for SDR SDRAM Memory         6.1.2       Support for SDR SGRAM Memories         6.1.3       Support for DDR SDRAM Memories                                         |                                                                                                                                                                            |

| 6.1 Overview<br>6.1.1 Support for SDR SDRAM Memory<br>6.1.2 Support for SDR SGRAM Memories                                                                                                                        |                                                                                                                                                                            |

| <ul> <li>6.1 Overview</li> <li>6.1.1 Support for SDR SDRAM Memory</li> <li>6.1.2 Support for SDR SGRAM Memories</li> <li>6.1.3 Support for DDR SDRAM Memories</li> <li>6.2 Memory for 64-Bit Interface</li> </ul> |                                                                                                                                                                            |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   |                                                                                                                                                                            |

| <ul> <li>6.1 Overview</li> <li>6.1.1 Support for SDR SDRAM Memory</li> <li>6.1.2 Support for SDR SGRAM Memories</li> <li>6.1.3 Support for DDR SDRAM Memories</li> <li>6.2 Memory for 64-Bit Interface</li></ul>  |                                                                                                                                                                            |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>59<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>62<br>62<br>63<br>66<br>66                                                       |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   |                                                                                                                                                                            |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>59<br>59<br>60<br>61<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>63<br>63<br>66<br>66<br>69<br>71                                                 |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>59<br>59<br>60<br>61<br>61<br>61<br>61<br>62<br>62<br>62<br>63<br>63<br>66<br>66<br>69<br>71<br>71                                                 |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>63<br>63<br>66<br>69<br>71<br>71<br>71                                                 |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62                                     |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>63<br>63<br>66<br>66<br>71<br>71<br>71<br>71 |

| <ul> <li>6.1 Overview</li></ul>                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>59<br>59<br>60<br>61<br>61<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62<br>62                                           |

| 7 Video BIOS                                                                                                     |                   |

|------------------------------------------------------------------------------------------------------------------|-------------------|

| 7.1 Overview                                                                                                     |                   |

| 7.2 BIOS Interface                                                                                               |                   |

| 7.2 BIOS Interface                                                                                               |                   |

| 7.2.1 Configuration for Parallel EEPROM                                                                          |                   |

| 7.2.3 ROM Chip Select - ROMCS#                                                                                   |                   |

|                                                                                                                  |                   |

| 7.2.4 EEPROM<br>7.2.5 Straps on the GPIO lines                                                                   |                   |

|                                                                                                                  |                   |

|                                                                                                                  |                   |

| 8 Crystal Oscillator and Clock Pins (XTALIN and XTAL                                                             | OUT)              |

| 8.1 Mode 1: External CMOS-Compatible Clock Input                                                                 |                   |

|                                                                                                                  |                   |

|                                                                                                                  |                   |

| 8.3 Application Notes                                                                                            | 82                |

|                                                                                                                  |                   |

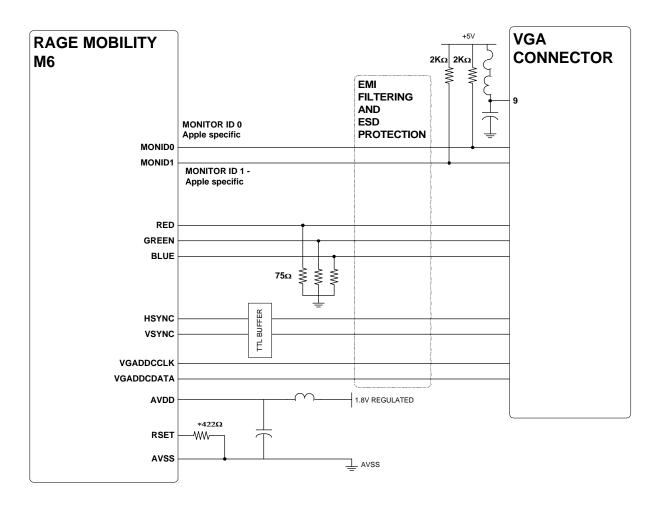

| 9 Analog Display                                                                                                 |                   |

| 9.1 Block Diagram                                                                                                |                   |

| 9.2 CRT Interface                                                                                                |                   |

| 9.2.1 Filtering                                                                                                  |                   |

| 9.2.2 ESD Protection                                                                                             |                   |

| 9.2.3 RGB Termination                                                                                            |                   |

| 9.2.4 Horizontal and Vertical Syncs                                                                              |                   |

| 9.2.5 DDC Interface                                                                                              |                   |

| 9.2.6 VGA Connector                                                                                              |                   |

| 9.3 DAC Interface                                                                                                |                   |

| 9.3.1 AVDD and A2VDD                                                                                             |                   |

| 9.3.2 AVSS and A2VSS                                                                                             |                   |

| 9.3.3 RSET and R2SET                                                                                             |                   |

|                                                                                                                  |                   |

| 10 Digital Flat Panel Interface                                                                                  | 87                |

|                                                                                                                  |                   |

| 10.1 Overview                                                                                                    |                   |

| 10.2 Integrated LVDS interface                                                                                   |                   |

| 10.2.1 Data and Clock Analog Differential Pairs - TXOUT and TXCLK                                                |                   |

| 10.2.2 Power and Grounds Pins – LPVDD, LPVSS, LVDDR, LVSSR                                                       |                   |

| 10.2.3 Unused Pins                                                                                               |                   |

| 10.3 Integrated TMDS interface                                                                                   |                   |

| 10.3.1 PCB Layout                                                                                                |                   |

| 10.3.1.1 Placement of Components                                                                                 |                   |

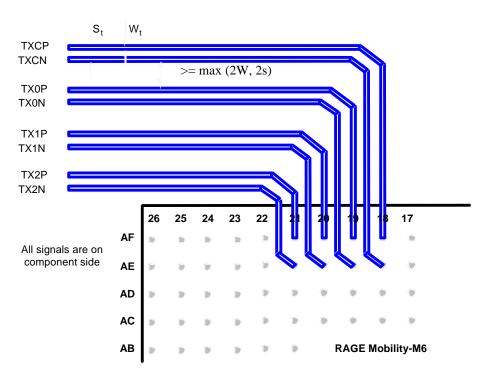

| 10.3.1.2 Routing TMDS Lines                                                                                      |                   |

| 10.3.1.3 Impedance Considerations                                                                                |                   |

| 10.3.1.4       Using Shields to Guard Against EMI and Cross talk         10.3.1.5       Power Source Cleanliness |                   |

| 10.3.1.6 Trace Parameter Calculations                                                                            |                   |

| 10.3.1.7 Using the DFP TMDS Calculator                                                                           |                   |

| 10.3.1.8 Using Numerical Analysis                                                                                |                   |

| 10.3.1.9 Sample Trace Parameter Calculations for Different Boards                                                |                   |

| 10.3.2 Data and Clock Analog Differential Pairs - TX and TXC                                                     |                   |

| 10.3.3 Hot Plug Detect - HPD                                                                                     |                   |

| 10.3.4 DDC Clock and DDC Data – DVIDDCCLK and DVIDDCDATA                                                         |                   |

| 10.3.5 Power and Ground Pins – TPVDD, TXVDDR, TPVSS, TXVSSR                                                      |                   |

| 10.3.6 Unused Pins                                                                                               |                   |

| ã 2000 ATI Technologies Inc.                                                                                     | Table of Contents |

RAGE MOBILITY M6 Graphics Subsystem Design Guide

| 10.4 La | yout Guidelines for Differential Signals     |    |

|---------|----------------------------------------------|----|

| 10.4.1  | Suppression of Common-Mode Noise             |    |

| 10.4.2  | Layout Considerations                        | 97 |

| 10.4.3  | Trace Routing                                |    |

| 10.4.4  | Trace Shielding                              |    |

| 10.5 TV | ' Out Interface                              |    |

| 10.5.1  | Component Placement                          |    |

| 10.5.2  | Ground Plane                                 |    |

| 10.5.3  | Power Plane                                  |    |

| 10.5.4  | Device Decoupling                            |    |

| 10.5.5  | Power Supply Decoupling                      |    |

| 10.5.6  | Digital Signals Interconnect                 |    |

| 10.5.7  | Analog Signal Interconnects                  |    |

| 10.6 Ex | ternal TMDS interface                        |    |

| 10.6.1  | Component Placement, ground and power planes |    |

| 10.6.2  | Digital Signals Interconnect                 |    |

| 10.6.3  | Analog Signal Interconnects                  |    |

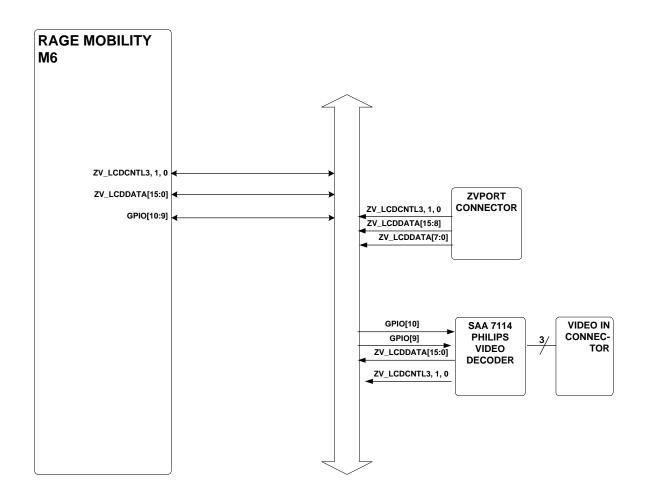

| 11 ATI Multimedia Interface                                            |       |

|------------------------------------------------------------------------|-------|

| 11.1 Overview                                                          |       |

| 11.2 DVS Port                                                          |       |

| 11.2.1 DVS Clock – ZV_LCDCNTL[3]<br>11.2.2 DVS Data – ZV_LCDDATA[15:0] |       |

| 11.2.2 DVS Data – ZV_LCDDATA[15:0]                                     |       |

| 11.2.3 Unused DVS Pins                                                 |       |

| 11.3 Software I2C Bus                                                  |       |

| 11.3.1 I2C Data - GPIO[9]                                              |       |

| 11.3.2 I2C Clock - GPIO[10]                                            |       |

| 12 Spread Spectrum Layout Guideline                                    | s 105 |

| 13 Revision History                                                    |       |

## Table of Figures

| Figure 1: RAGE MOBILITY M6 Graphics Subsystem                                      | 12 |

|------------------------------------------------------------------------------------|----|

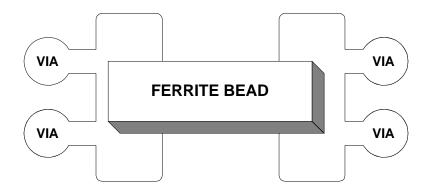

| Figure 2: Typical Installation for a Ferrite Bead                                  | 28 |

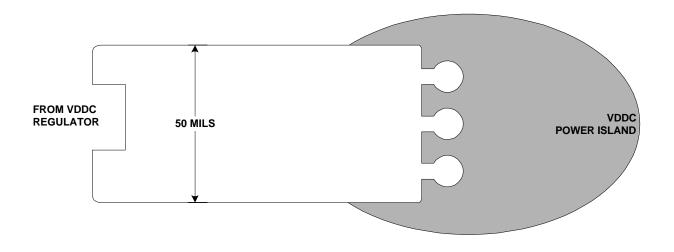

| Figure 3: Split Power Plane                                                        | 28 |

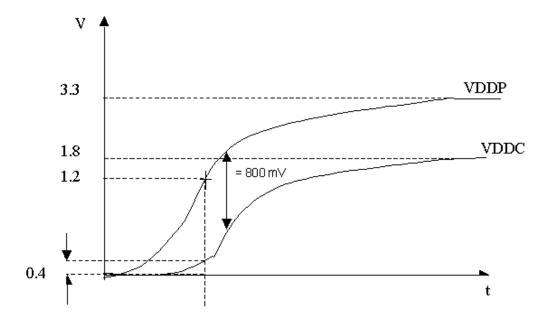

| Figure 4 Power sequence when VDDC derives from VDDR                                | 31 |

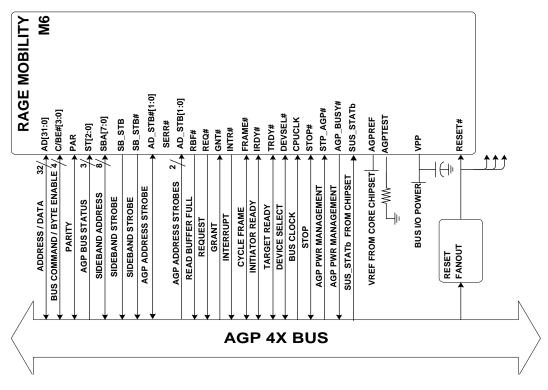

| Figure 5: AGP Interface Block Diagram                                              | 32 |

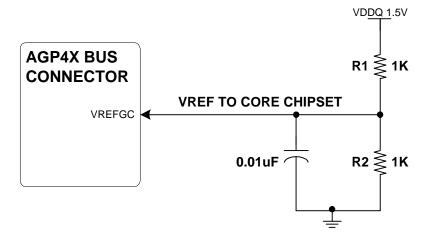

| Figure 6: VREF Voltage Divider Circuit                                             | 36 |

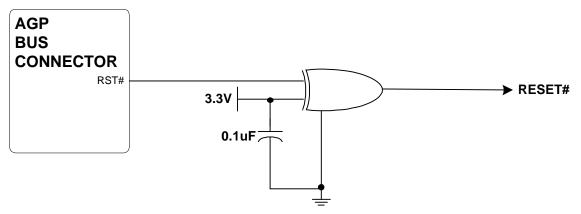

| Figure 7: RESET Buffer Circuit                                                     |    |

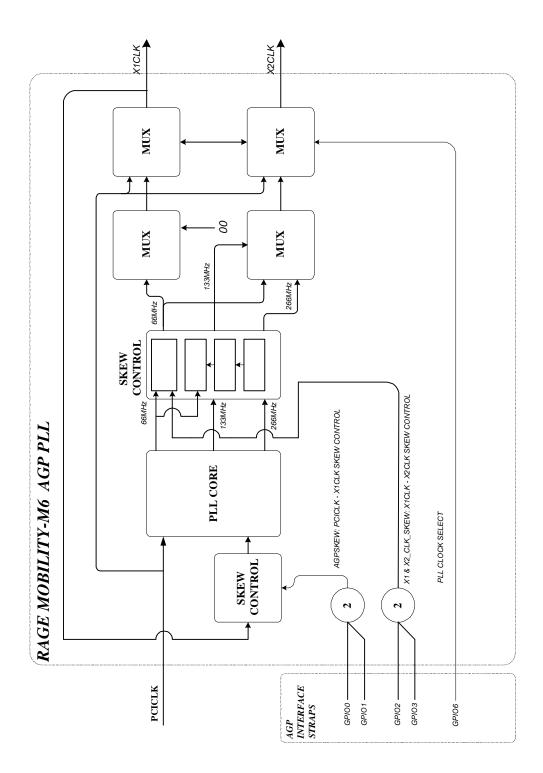

| Figure 8: AGP Bus: Clock Selection and Skew Control                                | 49 |

| Figure 9: PLL Interface                                                            |    |

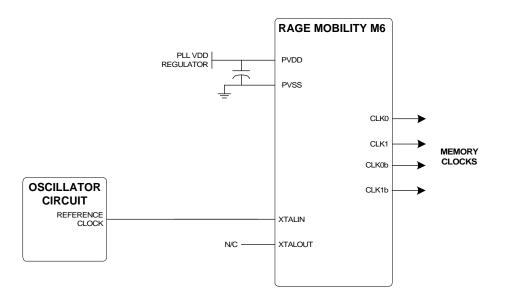

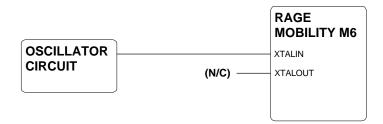

| Figure 10: RAGE MOBILITY M6 with Oscillator                                        | 55 |

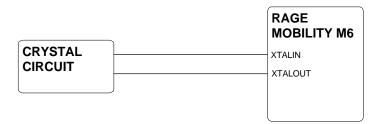

| Figure 11: RAGE MOBILITY M6 with Crystal                                           | 55 |

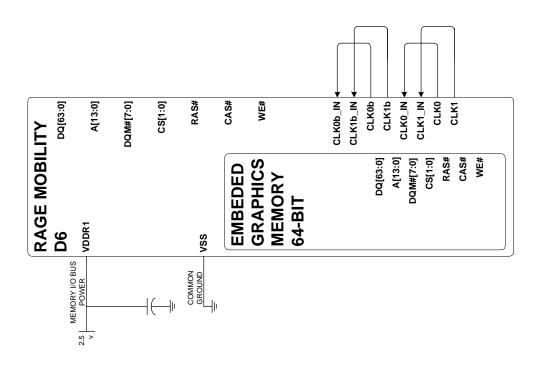

| Figure 12: Graphics Memory Interface – 64 Bit                                      | 59 |

| Figure 13: Graphics Memory Interface – 32 Bit                                      | 61 |

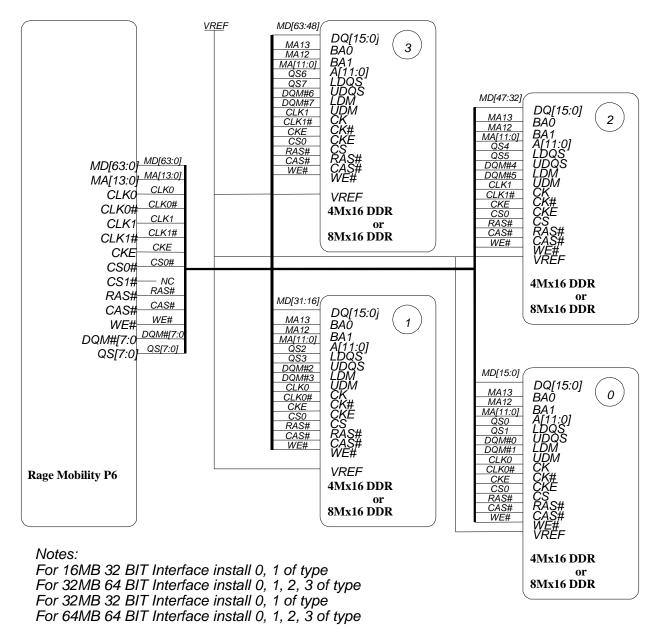

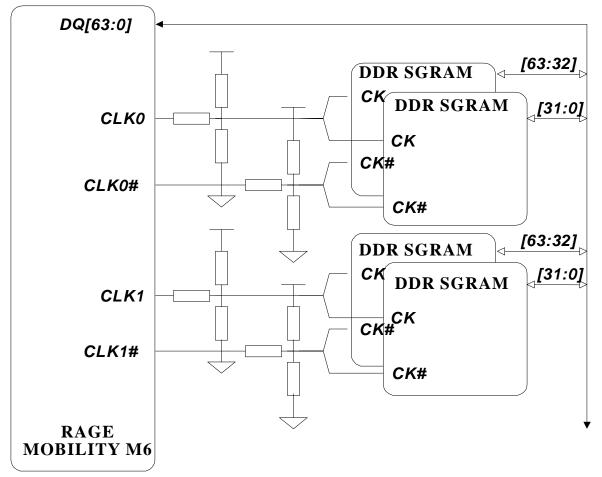

| Figure 14 DDR SDRAM Configuration                                                  | 63 |

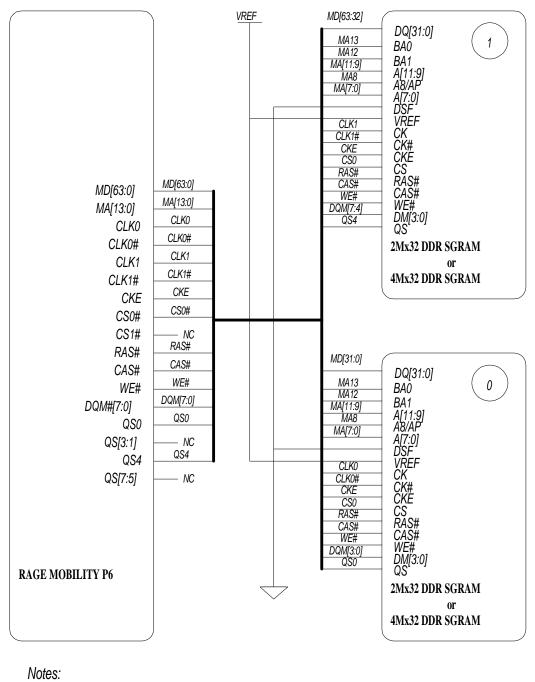

| Figure 15: DDR SGRAM Configuration                                                 | 64 |

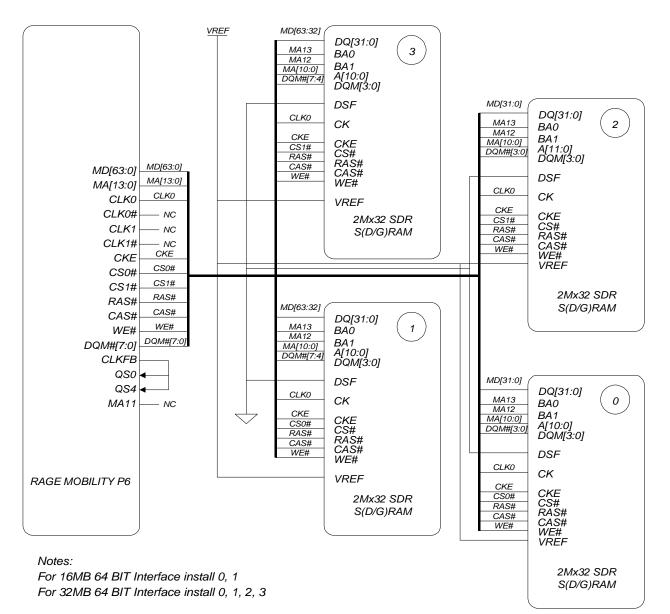

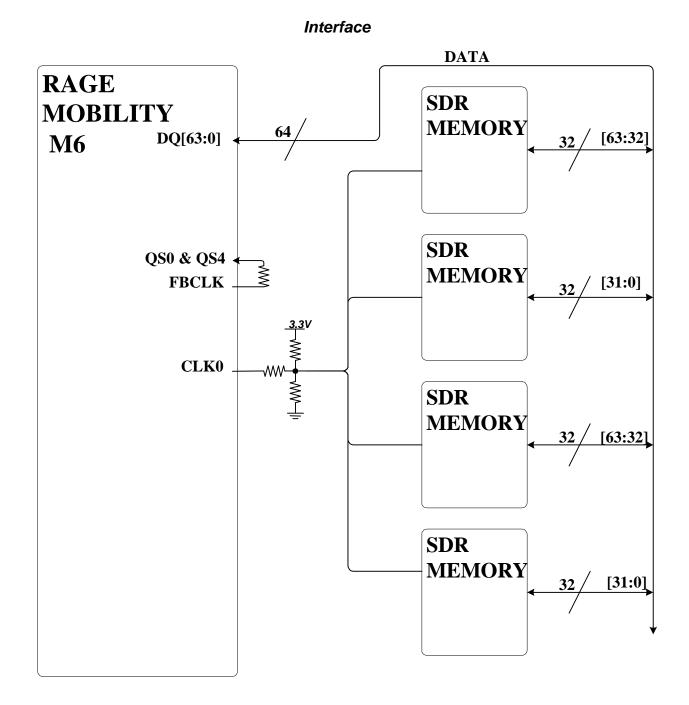

| Figure 16: SDR S(D/G)RAM configuration                                             | 65 |

| Figure 17: Memory Clock: Termination and Distribution for the 64-Bit DDR Interface | 66 |

| Figure 18: Memory Clock: Termination and Distribution for the 64-Bit SDR Interface | 67 |

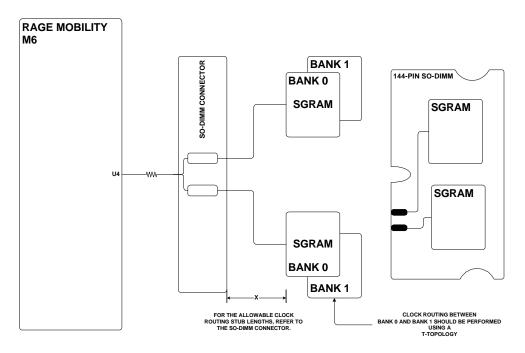

| Figure 19: Memory Clock Routing                                                    | 68 |

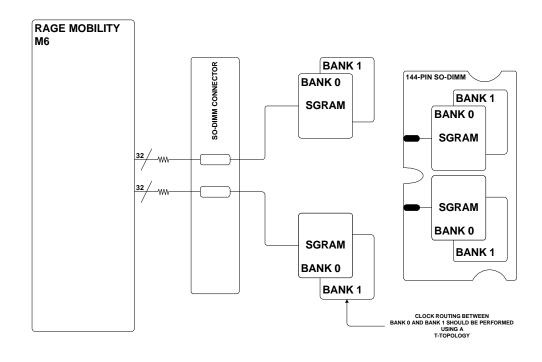

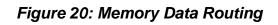

| Figure 20: Memory Data Routing                                                     | 70 |

| Figure 21: Address and Control Routing                                             | 70 |

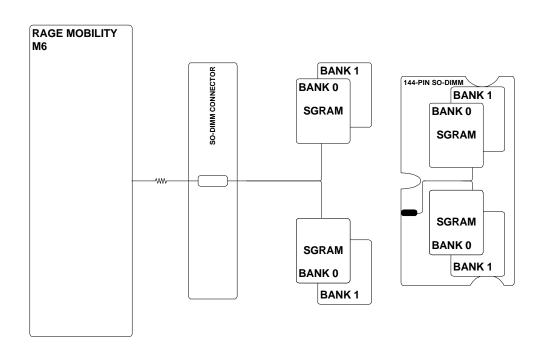

| Figure 22: Clock pair shielding                                                    | 72 |

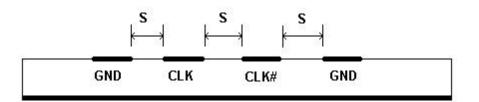

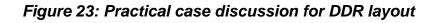

| Figure 23: Practical case discussion for DDR layout                                | 73 |

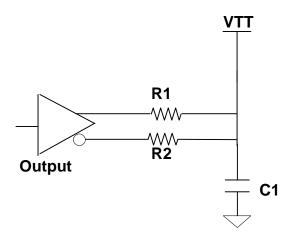

| Figure 24: Class II SSTL-2 DDR termination                                         | 74 |

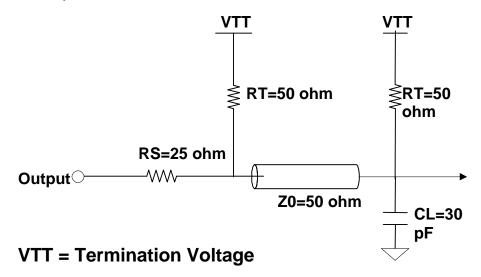

| Figure 25: Rage Mobility M6 DDR termination                                        | 74 |

| Figure 26: Independent termination for clock signals                               | 75 |

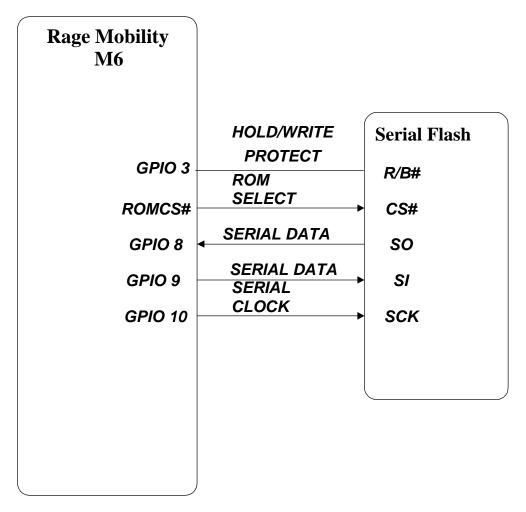

| Figure 27: BIOS Interface – Serial EEPROM Configuration                            | 77 |

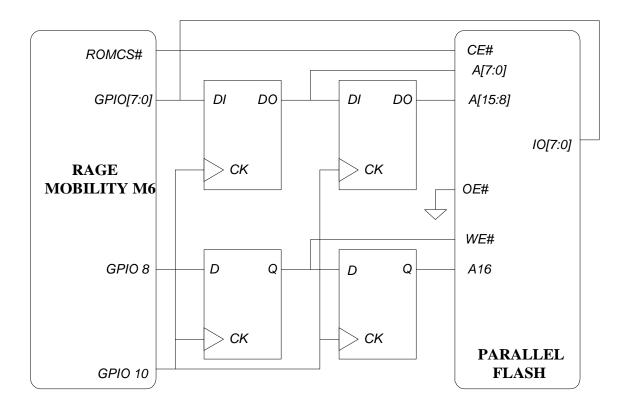

| Figure 28: BIOS Interface – Parallel EEPROM Configuration                          | 78 |

| Figure 29 Straps Implementation                                                    | 79 |

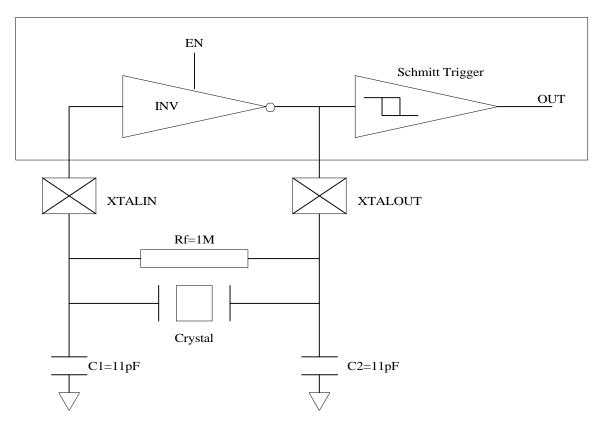

| Figure 30: Oscillator Circuit                                                      | 81 |

| Figure 31: Analog Display Section                                                  | 83 |

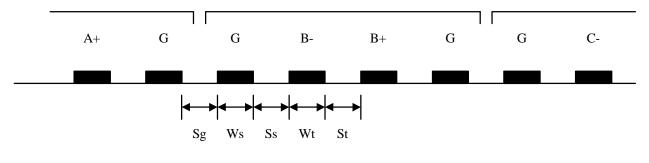

| Figure 32: Routing TMDS Lines                                                      | 89 |

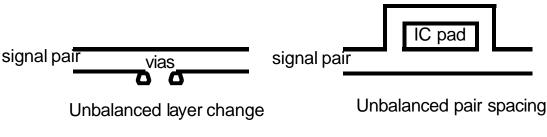

| Figure 33: Avoid Unbalanced Layer Change                                           | 90 |

| Figure 34: A Test Point                                                            | 90 |

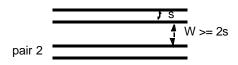

| Figure 35: Avoiding Cross talk                                                     | 91 |

| Figure 36: Guarded Differential Pair                                               | 91 |

|                                                                                    |    |

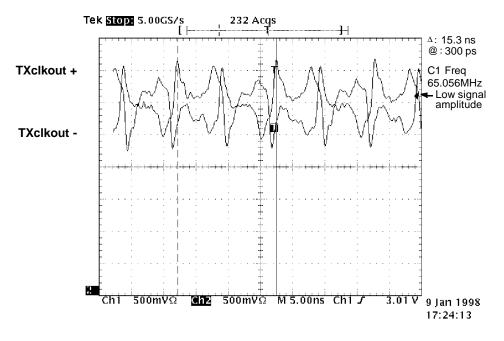

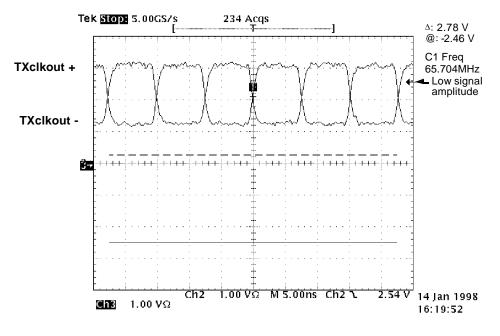

| Figure 37: Waveform polluted by Unstable Power | 92  |

|------------------------------------------------|-----|

| Figure 38: Clear TXCLK Output                  | 92  |

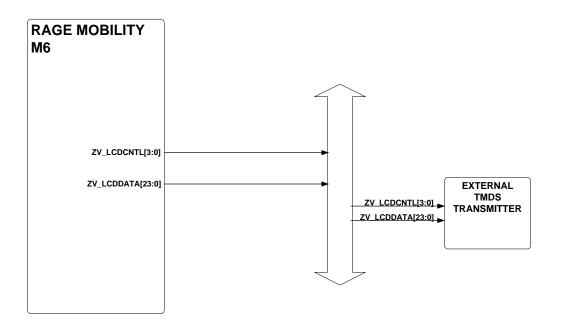

| Figure 39: External TMDS support               | 100 |

| Figure 40: ATI Multimedia Interface            | 102 |

| Figure 41: SM530 Single Power Plane Layout     | 105 |

## Table of Tables

| Table 1: Supported RAGE MOBILITY Controllers                        | 10  |

|---------------------------------------------------------------------|-----|

| Table 2: Optionally Unused Pins                                     | 15  |

| Table 3: Current Consumption                                        | 25  |

| Table 4: Trace Lengths (8/16MB) - AGP Signals (Group 1)             | 38  |

| Table 5: Trace Lengths (8/16MB)- AGP Signals (Group 2)              |     |

| Table 6: Trace Lengths (8/16MB) - AGP Signals (Group 3)             | 40  |

| Table 7: Trace Lengths on P6 - AGP Signals (Group 1)                | 41  |

| Table 8: Trace Lengths on P6 - AGP Signals (Group 2)                | 42  |

| Table 9: Trace Lengths on P6 - AGP Signals (Group 3)                | 43  |

| Table 10: Bus Configuration Straps                                  | 47  |

| Table 11: AGP Skew                                                  | 47  |

| Table 12: Clock Skew Straps                                         | 50  |

| Table 13: Clocks                                                    | 53  |

| Table 14: Supported SDR SDRAM                                       |     |

| Table 15: Supported SDR SGRAM                                       | 58  |

| Table 16: Load conditions for memory signals                        | 71  |

| Table 17: Control signals line length                               | 72  |

| Table 18: Method 1 - Fix Zdiff and feed in s and calculate Zo and W | 94  |

| Table 19: Method 2 - Feed in s and W and calculate Zdiff and Zo     | 94  |

| Table 20: Example Differential Pair Trace Calculations              | 95  |

| Table 21: Multimedia Channels                                       |     |

| Table 22: Video Port Pins Multiplexing                              | 103 |

## Table of Equations

| Equation 1: Propagation Delay | .37 |

|-------------------------------|-----|

| Equation 2: Zdiff             | .93 |

| Equation 3: Zo and W          | .93 |

| Equation 4: Zdiff and Zo      | .93 |

| Equation 5: W and s           | .93 |

| Equation 6: Zo and s          | .94 |

## 1 Introduction

#### 1.1 About This Manual

Use this manual along with the RAGE MOBILITY M6 Reference Design Schematics to help you design a graphics subsystem based on ATI's RAGE MOBILITY M6 graphics controller. This manual is intended for experienced design engineers.

#### 1.2 Scope

This manual should be used with the RAGE MOBILITY M6 Reference Design Schematics. Use this manual to help you integrate the RAGE MOBILITY M6 graphics controller into a motherboard-based graphics subsystem or into an add-in graphics adapter. The content of this manual focuses on general design considerations for:

• Component layout.

- Power and grounding requirements.

- Signal routing and termination.

- Configuration and feature options.

• Noise filtering.

• Exceptions and deviations (and their potential effects).

To ensure the integrity and robustness of your RAGE MOBILITY M6-based graphics subsystem, adhere to the recommendations of this manual.

## **1.3 Supported Controllers**

This manual supports the following types of RAGE MOBILITY controllers:

| RAGE MOBILITY M6<br>Graphics Controller<br>Model | BGA<br>Package | Reference<br>Schematic P/N | Graphics Controller<br>Specification P/N |

|--------------------------------------------------|----------------|----------------------------|------------------------------------------|

| RAGE MOBILITY P6                                 | 484-pin        | 105-REF88-00C              | CHS-216M6-00-01                          |

| RAGE MOBILITY M6                                 | 484-pin        | 105-REF87-00C              | CHS-216M6-00-01                          |

| RAGE MOBILITY D6                                 | 484-pin        | 105-REF87-00C              | CHS-216M6-00-01                          |

## 2 Graphics Subsystem Overview

This section is an overview of a RAGE MOBILITY M6-based graphics subsystem. Some aspects of this section will overlap with other sections. The remaining sections provide additional details regarding each specific interface. A graphics subsystem can be viewed as a collection of interfaces (functional blocks) to a graphics controller. The supported functions will depend on the features supported by a specific graphics controller.

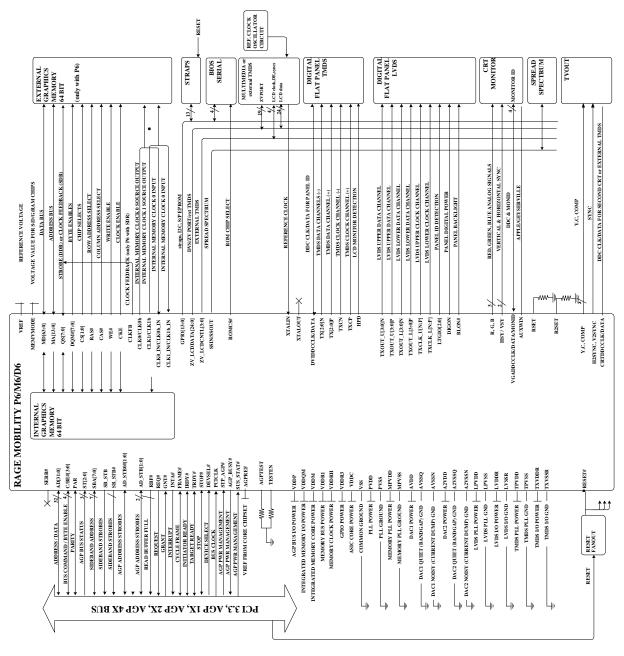

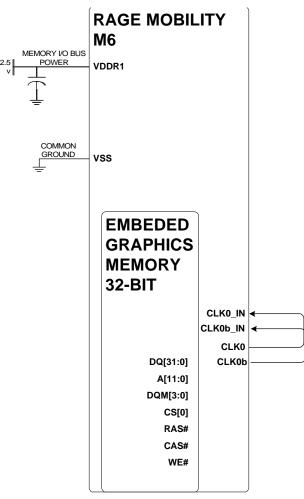

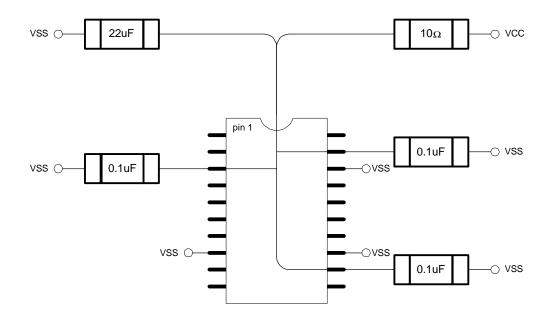

Figure 1: RAGE MOBILITY M6 Graphics Subsystem

## 2.1 Considerations for the Layout of the Subsystem

High-speed digital signals can generate large ground-current spikes that appear on the circuit's noise floor. Use the following guidelines so that the digital signals will be properly bypassed, kept away from sensitive circuit areas, and analog supplies.

- Keep digital signals away from analog signals.

- Keep digital components and wires as far away from analog sections as possible.

- Avoid routing digital signals through analog sections.

- Keep sensitive nets short by placing analog components close to the chip, and short wires over their respective planes. Keep a careful watch on RSET, R2SET, XTALIN, and XTALOUT signals.

- Place bypass capacitors as close as possible to each power pin.

- For 4-layer PCBs, position the ground plane closest to the component side and position the power plane closest to the solder side.

- For add-in board designs, join all ground nets at one location as close as possible to the card edge connector.

- Use a low impedance ground (i.e., a continuous ground plane).

- Provide separate filtered power supplies for analog functions.

- To reduce EMI and comply with FCC requirements, install capacitors and ferrite beads on the RGB signals.

- When routing the AGP interface signals, closely follow the AGP specification.

- Avoid using sockets.

- To reduce path impedance, use multi-via pads for power and ground pad connections.

- Keep trace lengths as short as possible.

- To minimize cross talk, sandwich all high-frequency signal traces between ground traces or planes.

- For traces that carry high-frequency signals, avoid using sharp corners or bends.

## 2.2 Subsystem Grounding

Uniform ground planes is the preferred grounding topology because macros are given a solid ground reference.

Uniform grounding minimizes the ground bounce due to switching currents.