# Mobility M6 Pinout Specifications

# **Technical Reference Manual**

© 2000 ATI Technologies Inc.

# CONFIDENTIALWASERIAL

All information contained in this man, all s confidential material of ATI Technologies Inc. Unauthorized the ordisclosure of the information contained herein is prohibited

You may be held responsible or any loss or damage suffered by ATI for your unauthorized disclosure ereon in whole or in part. Please exercise the following precaptions

- Store all hand copy sin a secure place when not in use.

- Save an electronic copies on password protected systems.

- Do not reproduce or distribute any portions of this manual in paper or electronic form (except as permitted by ATI).

- Do not pust this manual on any LAN or WAN (except as permitted by ATI).

our projection of the information contained herein may be subject to periodic audit by ATI. This manual is subject to possible recall by ATI.

The information contained in this manual has been carefully checked and is believed to be entirely reliable. No responsibility is assumed for inaccuracies. ATI reserves the right to make changes at any time to improve design and supply the best product possible.

ATI, *mach64*, **3D RAGE**, **RAGE THEATER**, **RAGE 128**, **RADEON** are trademarks of ATI Technologies Inc. All other trademarks and product names are properties of their respective owners.

# **Record of Revisions**

| Version     | Date     |

|-------------|----------|

| First Draft | Jun 2000 |

# **Table of Contents**

## **Chapter 1: Features Overview**

| 1.1 | Introdu | cing M6                                      | 1-1  |

|-----|---------|----------------------------------------------|------|

| 1.2 | General | and Interfacing Features                     | 1-2  |

| 1.3 | Feature | s in Details                                 | 1-4  |

|     | 1.3.1   | 2D Acceleration Features.                    |      |

|     | 1.3.2   | 3D Acceleration Features.                    | 1-5  |

|     | 1.3.3   | TCL (Transform, Clip, and Lighting) Features |      |

|     | 1.3.4   | Motion Video Acceleration Features.          |      |

|     | 1.3.5   | Zoom Video Port Features                     | 1-9  |

|     | 1.3.6   | Dual Display Features                        |      |

|     | 1.3.7   | Integrated LVDS                              |      |

|     | 1.3.8   | Bus Support Features                         |      |

|     | 1.3.9   | Memory Support Features                      |      |

|     | 1.3.10  | Power Management Features                    |      |

|     | 1.3.11  | PC Design Guide Compliance                   |      |

|     | 1.3.12  | Test Capability Features                     |      |

| 1.4 | Display | Modes                                        | 1-14 |

|     | 1.4.1   | 2D Display Modes                             |      |

|     | 1.4.2   | 3D Modes.                                    |      |

| 1.5 | Softwar | re Features                                  | 1-18 |

#### Chapter 2: Pin and Strap Descriptions

| 2.1 | Pin Count by Functional Group                 | 2-2  |

|-----|-----------------------------------------------|------|

| 2.2 | Pin Assignment                                |      |

|     | 2.2.1 M6 Pin Assignment Top View (Left Half)  |      |

|     | 2.2.2 M6 Pin Assignment Top View (Right Half) |      |

| 2.3 | AGP/PCI Host Bus Interface                    | 2-5  |

| 2.4 | Bus Power Management Interface                | 2-9  |

| 2.5 | Memory Interface (SGRAM, SDRAM)               | 2-11 |

| 2.6 | Zoom Video Port / External TMDS Interface     | 2-12 |

| 2.7 General  | l Purpose I/O Interface              |      |

|--------------|--------------------------------------|------|

| 2.8 LCD G    | eneral Purpose I/O Interface         | 2-12 |

| 2.9 LVDS     | Interface                            |      |

| 2.10 LVDS    | Power and Ground Interface           | 2-15 |

| 2.11 Extern  | al SSC                               |      |

| 2.12 Panel   | Control                              |      |

| 2.13 TMDS    | S Interface                          |      |

| 2.14 DAC     | (CRT) Interface                      | 2-17 |

| 2.15 DAC2    | 2 (TV/CRT2) Interface                |      |

| 2.16 Test In | nterface                             |      |

| 2.17 ROM     | Interface                            | 2-19 |

| 2.18 PLLs    | and Crystal Interface                |      |

| 2.19 Host F  | Power Interface                      |      |

| 2.20 Memo    | ry Power Interface                   |      |

|              | ower Interface                       |      |

| 2.22 Core I  | Power Interface                      |      |

| 2.23 Groun   | d Interface                          |      |

| 2.24 M6 St   | raps                                 |      |

| 2.24.1       | Pin Based Straps                     |      |

| 2.24.2       | ROM Based Straps                     |      |

| 2.24.3       | Strap Latching and Wake-Up Procedure |      |

| 2.24.4       | Readback of Strap Settings.          |      |

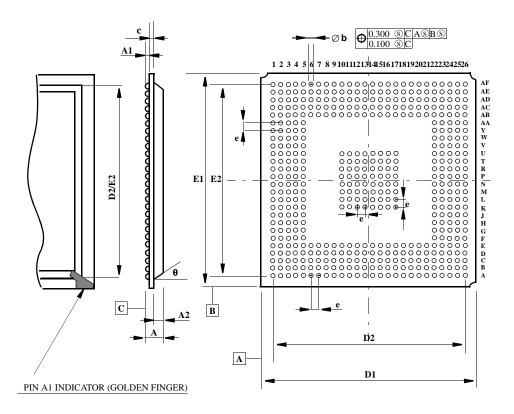

# Chapter 3: Physical Dimensions

| 3.1 M6 Physical Dimensions |

|----------------------------|

|----------------------------|

# Appendix A: Pin Listings

| A.1 | M6 Pin List Sorted by Ball Reference. | A-2  |

|-----|---------------------------------------|------|

| A.2 | M6 Pin List Sorted by Signal Name     | A-10 |

# **Chapter 1** Features Overview

# 1.1 Introducing M6

#### Maximum 2D & 3D Performance

M6 provides the fastest available 2D, 3D, and multimedia graphics performance for today's applications in full 32-bit color. Its 3D architecture also includes unprecedented innovations that enable advanced new features in upcoming applications, without compromising performance. With flexible memory support, M6 permits implementations targeted at both gaming enthusiast and workstation platforms.

#### Charisma Engine™

M6's Charisma Engine<sup>TM</sup> is the world's fastest geometry processing unit and is also the first to incorporate acceleration for advanced character animation features, including 4-matrix skinning and keyframe animation. These effects are critical for enabling game characters to display life-like facial expressions and to achieve fluid movement and motion.

#### Pixel Tapestry<sup>TM</sup> Architecture

M6 delivers the fastest 32-bit color rendering performance available, and supports three-way multitexturing and new 3D effects without compromising speed. The Pixel Tapestry<sup>TM</sup> Architecture is the first to be able to process up to 3 textures per pixel in a single clock cycle, bringing 3D worlds to life with incredible detail and realism. It easily deals with complex elements such as metals, liquids and wood and their interactions with lights and shadows.

#### **Comprehensive Digital Video Support**

M6 integrates industry leading digital video features, including advanced deinterlacing algorithms for unprecedented video quality and integrated digital TV decode capability. Combined with a tuner and demodulator, M6 provides an all-format DTV/HDTV solution, even including the 1920 pixel wide 1080i format. Coupled with the RAGE THEATER analog encoder/decoder chip, M6 provides a complete convergence solution.

#### **Ideal for Windows 2000**

M6 provides comprehensive support for all new Windows 2000 display-oriented features,

including acceleration of new GDI extensions like Alpha BLTs, Transparent BLTs, and Gradient Fills, as well as exclusive, patent-pending hardware alpha cursor support.

#### Flexible, High Performance Memory Support

M6 incorporates support for single or double data rate SDRAM/SGRAM at up to 200MHz, giving memory bandwidth of up to 6.4GB/s. Since memory bandwidth is increasingly becoming the largest barrier to performance in today's and tomorrow's most advanced applications, M6 features new HyperZ<sup>TM</sup> technology to boost effective memory bandwidth by over 20%.

# **1.2 General and Interfacing Features**

- 32-bit PCI bus (Rev 2.2), 3.3 V with bus mastering support.

- Comprehensive AGP support including 3.3 Volt (AGP 2X) and 1.5 Volt (AGP 4X) mode operation, sideband addressing, AGP texturing (direct memory execution), and support for AGP reads and writes.

- Single channel 64-bit memory interface using SGRAM or SDRAM to build 8/16/32/64/128 MB configurations. Operating frequency is 125MHz minimum to 200MHz maximum, SDR or DDR. Gives memory bandwidth of up to 6.4GB/s.

- Support for ROM or Flash RAM parallel or serial video BIOS.

- Two independent CRT controllers to support two asynchronous simultaneous display paths.

- Integrated DAC for CRT with stereoscopic display support.

- Integrated second DAC for the second CRT support.

- Integrated TMDS transmitter running up to 165MHz for support up to 1600x1200 at 60Hz. Fully compliant with DVI and DFP connection standards.

- Support for external TMDS transmitter via 24-bit digital output to drive most popular TMDS transmitters up to 165MHz frequency

- Integrated dual channel LVDS interface up to 85MHz per channel. Supports up to QXGA resolution.

- Integrated enhanced TV encoder with 10-bit DAC (shared between second CRT DAC and TV)

- Independent DDC lines for both DACs and TMDS connections. Also full AppleSense support on DAC connection.

- External Spread Spectrum support for LVDS link to reduce EMI.

- Static and dynamic Power Management support (APM as well as ACPI) with full VESA DPMS and Energy Star compliance.

- Support for 8-bit and 16-bit video capture port including ZV port.

- Comprehensive testability including full internal scan, memory BIST, I/O xor tree and Iddq.

- Comprehensive 3D geometry acceleration capabilities, including transform, clipping, and lighting.

- Integrated geometry engine.

- Ideal accelerator for Windows 2000 includes patent pending hardware support for the Windows 2000 alpha cursor, as well as acceleration of new GDI extensions such as Alpha BLTs, Transparent BLTs, and Gradient Fills.

- Integrated digital TV decode capability. Combined with a tuner an demodulator, M6 provides an all-format DTV/HDTV solution, including the 1920 pixel wide 1080i format.

- Fully compliant with expected PC 2001 requirements.

- Full ACPI 1.0b, OnNow, and IAPC (Instantly Available PC) power management, including PCI power management registers.

- Bi-endian support for compliance on a variety of processor platforms.

- Unique enhanced TCA (Triple-Cache Architecture) incorporates texture, pixel and vertex caches to maximize effective memory bandwidth.

- CCE high-speed pull architecture software interface optimized for Pentium III and Athlon systems:

- Bus mastering of 2D&3D display lists.

- Direct walk of Direct3D/OpenGL vertex list.

- Ultra-thin driver layer.

- Maximizes concurrency between RAGE 6 and host.

- Optimized for Pentium II SSE and AMD 3DNow! processor instructions.

- Triple 10-bit palette DAC supports pixel rates to 350MHz.

- DVI-compliant integrated 165MHz TMDS transmitter.

- Up to UXGA (1600x1200) resolution.

- Supports VESA proposed reduced blanking timings.

- Ratiometric expansion.

- DDC1 and DDC2ci for plug and play monitors.

- Supports optional RAGE Theater companion chip for NTSC/PAL TV out and NTSC/PAL/SECAM analog video capture.

- Flexible memory support:

- SGRAM or SDRAM.

- SDR or DDR.

- DDR support for both system memory SDRAM and graphics SGRAM devices.

- 16MB to 128MB.

- High performance memory interface

- 6.4GB/s with 200MHz DDR.

- 3.2GB/s with 200MHz SDR.

- Dual independent channels maximize memory efficiency.

- Integrated hardware diagnostic tests performed automatically upon initialization.

- High quality components through at-speed testing, built-in Scan, Iddq, CRC, chip diagnostics, and NAND tree.

- Single chip solution in 0.18 micron, 1.8V CMOS technology in 649 BGA package.

- Comprehensive HDKs, SDKs and utilities augmented by full engineering support.

- Complete local language support (contact ATI for current list).

# **1.3** Features in Details

## **1.3.1 2D Acceleration Features**

- Highly-optimized 128-bit engine, capable of processing multiple pixels/clock. Higher speed compared to the RAGE 128 VR / GL chip due to various improvements.

- Hardware acceleration of Bitblt, Line Draw, Polygon / Rectangle Fill, Bit Masking, Monochrome Expansion, Panning/Scrolling, Scissoring, and full ROP support (including ROP3).

- Optimized handling of fonts and text using ATI proprietary techniques.

- Game acceleration including support for Microsoft's DirectDraw: Double Buffering, Virtual Sprites, Transparent Blit, and Masked Blit.

- Acceleration in 8/15/16/32 bpp modes.

- Significant increase in the High End Graphics WinBench score due to capability for C18 color expansion.

- Setup of 2D polygons and lines.

- Support for new WIN 2000 GDI extensions: Alpha BLT, Transparent BLT, Gradient Fill.

- Hardware cursor (up to 64x64x32bpp), with alpha channel for direct support of WIN 2000 alpha cursor

#### **1.3.2 3D Acceleration Features**

- Primitive (Triangle) set up rates of up to 20 Million triangles per second.

- 3D Texture support.

- Cubic Environment Mapping.

- Comphrehensive support for perturbation bump mapping (Tritech method): emboss, dot-product, and environment bump maps.

- Comprehensive enhanced 3D feature set:

- Improved precision in Anisotropic filtering and Bilinear filtering.

- Complete 3D primitive support: points, lines, triangles, lists, strips and quadrilaterals and BLTs with Z compare.

- Improved texture compositing, with no limitations on texture formats or location (i.e., one texture may reside in AGP memory and the other in frame buffer memory).

- Full screen or window double or triple buffering for smooth animation.

- Support of special effects such as simultaneous alpha blending and fog (vertex and z-based), video textures, texture lighting, reflections, shadows, spotlights, LOD biasing and texture morphing. Filtered texture alpha channel, and hardware support for D3D 'MODULATEALPHA' texture blending mode.

- Hidden surface removal using 16, 24, or 32-bit Z-buffering (maximum Z-buffer depth is 24 bits when stencil buffer enabled), 16 or 32-bit W-buffering.

- 8-bit stencil buffer.

- Line and Edge anti-aliasing.

- 4 bits of subpixel and subtexel accuracy.

- Gouraud and specular shaded polygons.

- Advanced texture mapping support.

- Perceptively correct per pixel mip-mapped texturing with LOD biasing and chroma-key support.

- Support point sampled, bilinear, trilinear and anisotropic filtering.

- Multi-texturing via three texture blending units, allowing 6 texel reads per pixel in a single tick and single pass. Allows effects such as: light and gloss maps, detail maps, reflections, shadows, spotlights, and texture morphing.

- 3D Textures

- Bilinear and trilinear texture filtering.

- Full support of Direct3D texture lighting.

- Dithering support in 16 bpp for near 24 bpp quality in less memory.

- Extensive 3D mode support:

- Draw in RGBA32, RGBA16, & RGB16.

- Texture map modes: RGBA32, RGBA16, RGB16, RGB8, ARGB4444, YC<sub>r</sub>C<sub>b</sub>444.

- Compressed texture modes: YC<sub>r</sub>C<sub>b</sub>422, CLUT4 (CI4), CLUT8 (CI8), VQ, and DX6 mode.

- Full scene sort independent anti-aliasing.

- DX6 Color Compression.

- Improved support for DX6 Blend mode.

- Control bit for Vertex Walker zero area.

- Support for 32 bpp Palette (similar to the RAGE PRO LCD).

- Improvement to Chroma Key functionality (similar to the RAGE PRO LCD).

- Support for OpenGL format for Indirect Vertices in Vertex Walker.

- Support for DirectX 6.0 compressed texture scheme (i.e., color cell compression) that allows for higher benchmark scores.

- Hardware Z-buffer clear support.

- Maximum performance on AGP 4X platforms.

- Improved sub-textel accuracy to improve the appearance of highly magnified textures).

- Maximum performance of OpenGL on AGP 4X platforms.

- Improved performance in Raw Rendering and Geometry due to higher engine speed.

- On-chip texture cache dramatically improves large triangle performance

- On-chip vertical cache eliminates unnecessary vertex reads.

- HyperZ technology dramatically improves performance by maximizing Z-buffer efficiency.

- Optimized for full performance in true color triple buffered 32bpp acceleration modes.

- Second generation SuperScalar Rendering engine provides top 3D performance.

- Support for Microsoft's next generation GDI+ user interface:

- Off axis 3D text readability improvement with anisotropic filtering.

- Arbitrary texture sizes up to 2048x2048.

### **1.3.3** TCL (Transform, Clip, and Lighting) Features

- Dedicated geometry acceleration for Direct3D and OpenGL.

- HW Transformation, clipping and lighting rates of over 25 million triangles per second.

- Transforms homogeneous vertices from Object / Model Coordinates to Clip Coordinates

- Performs Frustum Clipping on the Point / Line and Triangle Primitives in Clip Coordinates

- Performs Texture Coordinate Transformation

- Supports DirectX skinning, with a 4-matrix / 2 vertex Vertex Blending (Skinning / Morphing (Tweening))

- View volume clipping and up to six user defined clip planes.

- Supports Guard-Band Clipping for clipping performance optimization

- Supports DirectX / OpenGL Texture Coordinate Generation

- Supports 6 User-Defined Clip Planes. Performance Optimizations Based on Coordinate Systems

- Supports OpenGL / DirectX Directional (Infinite) Lighting with Infinite & Local Viewer. Up to 8 Lights. Includes DX7 color-per-vertex support.

- Supports OpenGL / DirectX Local Lighting with Infinite & Local Viewer. Up to 8 lights. Includes Range and Spot Attenuation, Includes DX7 color-per-vertex support.

- Supports Vertex Reuse capability for performance optimization of triangle lists

- Supports Back-Face Culling for performance optimization

- Supports polygon-id based shadow processing.

- Supports DirectX dual cone spot lights for DirectX lighting model.

- Supports normal re-normalization and constant rescale for DirectX/OpenGL lighting model.

- Supports separate and combined accumulation of diffuse and specular colors for DirectX/OpenGL lighting models.

- Supports derivation of alpha through lighting model calculations or directly from input diffuse color.

## 1.3.4 Motion Video Acceleration Features

- Video scaling and fully programmable YCrCb to RGB color space conversion for full-screen / full-speed video playback and fully adjustable color controls.

- Front and back end scalers plus capture port scaler to support multi-stream video for video conferencing and other applications.

- Front end scaler support for 8, 15, 16, and 32 bpp color depths.

- Back end overlay/scaler supports up to 8x4 tap filtering, and always ensures at least 4x2 tap filtering even in extreme cases. 4x4 tap is typical. Back-end scaler also supports upscaling and downscaling, filtered scaling of all supported YUV formats, RGB32 and RGB15/16, and filtered display of images up to 1920 pixels wide.

- Expanded line buffer allowing vertical filtering of native standard definition images.

- Enhanced MPEG-2 hardware decode acceleration, including support for both motion compensation and IDCT, to provide dramatically reduced CPU utilization without incurring the cost of a full MPEG-2 decoder. Also supports all format DTV/HDTV decode and top quality DVD with lowest CPU usage. This is superior to competing motion compensation solutions, including those marketed as '9-bit' motion compensation.

- Integrated high performance iDCT and motion compensation allows MPEG-2 decode of all 18 ATSC formats including 1280x720p and 1920x1080i on standard speed CPUs. It also allows "timeshifting" of standard definition television in standard systems by ensuring the CPU has enough remaining power to perform real-time MPEG-2 compression while the M6 handles most of the MPEG-2 decompression load.

- Hardware DVD subpicture decoder with interpolating scaler and alpha compositor to provide optimal DVD subpicture quality in all display bit depths.

- Adaptive de-interlacing filter eliminates video artifacts caused by displaying interlaced video on non-interlaced displays, by analyzing image and using optimal

de-interlacing function on a per-pixel basis. Also can be programmed to other methods such as bob, weave, and ATI enhanced weave.

- Bi-directional bus mastering engine with full YC<sub>r</sub>C<sub>b</sub> planar mode support for superior MPEG-2 decode and video conferencing.

- Enhanced support for range based graphics and video keying for effective overlay of video and graphics.

- Ability to genlock to any broadcast video signal, eliminating synchronization problems.

- YC<sub>r</sub>C<sub>b</sub> to RGB color space converter with support for both packed and planar YC<sub>r</sub>C<sub>b</sub> (YC<sub>r</sub>C<sub>b</sub>422, YC<sub>r</sub>C<sub>b</sub>410, YC<sub>r</sub>C<sub>b</sub>420). Increased user control over color characteristics, and improved precision and gamma correction for brighter, richer color.

- $YC_rC_b422$ ,  $YC_rC_b410$ ,  $YC_rC_b420$ , RGB32, RGB16/15 in back end scaler/overlay.

- Ability to reconstruct frames of field-based content when software indicates that content was originally progressive and has been converted via 3:2 pull down, provided that the decoder gives appropriate cues.

- Hardware mirroring for flipping mirror images in video conferencing systems.

## 1.3.5 Zoom Video Port Features

- ZV port (PCMCIA compliant with CCIR601 timing).

- Allows transfer of the video data directly into the frame buffer without loading down the PCI bus

- Dedicated video port guarantees video frame rates (30 frames per second)

- Maximum 40MHz, 16bpp YUV422 (PCMCIA specs 16MHz maximum)

# **1.3.6 Dual Display Features**

#### General

- Dual independent displays (LCD/LCD, LCD/CRT, LCD/TV, CRT/TV)

- Two triple 10-bit palette DACs with gamma correction for true WYSIWYG color. Pixel rates up to 300 MHz standard.

- Resolution, refresh rates and display data can be completely independent.

- Primary display path supports VGA and accelerated modes, video overlay, hardware cursor, hardware icon and palette gamma correction.

- Secondary display path supports accelerated modes, video overlay, hardware cursor, hardware icon and palette gamma correction. However, it does not support VGA.

- Video genlocking supported for both CRTCs.

- Single video overlay using back-end scaler is switchable between displays.

- Supports two new graphics formats: 16bpp aRGB 4444 and 16bpp alpha and index 88. Also supports 8/15/16/24/32 bpp graphics formats with gamma correction in all modes.

- Stereoscopic display capability.

- Support for auxilary window signal.

- Support for up to 4k x 4k resolution display.

- Support for DDC1 and DDC2B+ for plug and play monitors, and AppleSense monitor detection support.

- 8-bit alpha blending of graphics and video overlay.

- Hardware cursor up to 64x64 pixels in 2bpp, full color AND/XOR mix, and full color 8-bit alpha blend.

- Hardware icon up to 128x128 pixels in 2bpp.

- Virtual desktop support.

- Support for flat panel displays (see section on Fixed Resolution Display below for details).

#### TV Out

An integrated TV encoder with on-chip triple DAC allows simultaneous CRT/LCD/TV output with these outstanding TV-out characteristics:

- 10-bit DAC with 8-tap filter producing scaled, flicker removed, artifact suppressed display on a PAL or NTSC TV with Composite, S-Video, and RGB outputs.

- Support for Macrovision 7.02 copy protection standard (required by DVD players) a fully programmable timing capability, it will accommodate potential changes in the Macrovision algorithm without any hardware changes.

- YUV Direct/Passthrough mode for video/MPEG playback and DVD provides the best quality movie playback, it also allows titles to be displayed on TV with their original high quality and without any artifact from the TV-out circuit.

- Secondary display support for the RGB mode.

- 1024x768 32bpp support improved from ImpactTV2 to support up to 1024x768 mode. Modes supported include the 800x600 and 16:9 type display such as 848x480, with user flexibility for moving and sizing the screen.

- Line 21 Closed Caption and Extended Data Service support for encoding in Vertical Blanking Interval (VBI) of TV signal.

- CGMS-A DVD copy management support in VBI through Line-20 and/or Extended Data Service (Line-21 Field 2).

- UV filtering based on colour averaging results in a sharper picture as well as reduced flicker.

- ATI's exclusive "Composite Dot Crawl" freeze option for PAL and NTSC to improve picture quality.

- TV-out power management support.

# Features for Fixed Resolution (e.g. Flat Panel or Digital CRT) Display via integrated TMDS transmitter

- Supports DVI, DFP and VESA P&D interfaces with integrated TMDS transmitter.

- TMDS transmitter operates to 165 MHz and fully supports reduced blanking.

- Support for fixed resolution displays (e.g. panels) from VGA (640x480) to wide UXGA (1600x1200) resolution with full ratiometric expansion ability for source modes up to 1280x1024. Higher resolution panels and digital CRTs possibly supported. Contact ATI for details.

- Improved auto expansion.

- Optional auto-centering mode to display desktop at native size without ratiometric expansion.

- Support for VGA text modes in centering panel modes (up to approximately 165 MHz pixel frequency).

- Support for reduced blanking intervals, as defined by VESA.

## **1.3.7 Integrated LVDS**

- Integrated dual 112MHz LVDS interface.

- Single/dual channel QXGA resolution TFT panels.

- 32bpp TFT (QXGA) using dual channel LVDS.

- 784 Mbps/channel with 112 MHz pixel clock rate.

- 3 pairs (+1 clock) and 4 pairs (+1 clock) modes for both single and dual channel LVDS.

- FPDI-2 compliant; compatible with receivers from National Semiconductor, Texas Instruments, and THine.

- OpenLDI compliant excluding DC balancing.

- LVDS eye pattern to improve testability of LVDS module.

## **1.3.8 Bus Support Features**

- Comprehensive AGP support:

- 2X and 4X mode operation.

- Sideband Addressing.

- AGP Texturing (Execute mode).

- Both AGP reads and writes (without support for the 'fast write' capability defined in revision 2.0 of the AGP specification.

- AGP 1X mode operation.

- PCI version 2.2 with full bus mastering and scatter / gather support.

- 3.3 V and 5 V PCI interfaces. 5 V PCI only compatible with systems that ensure bus signals do not rise above 3.3 V typical. This works with all current standard system chipsets from Intel and other major suppliers.

- Support for AGP Power Management via AGP Busy protocol (1.61 as well as Solano2-M 0.1).

# **1.3.9 Memory Support Features**

- Supports a variety of memory configurations for bandwidths of up to 3.2 GB/s:

- SDRAM or SGRAM may be used for all memory configurations (32 or 64-bit).

- Single Data Rate (SDR), up to 200 MHz (1.6 GB/s at 64-bits).

- Double Data Rate (DDR), up to 200 MHz (3.2 GB/s at 64-bits).

- Flexible graphics memory configurations: 8MB up to 128MB SDR/DDR SGRAM or SDR SDRAM.

- Memory upgrade via industry standard SO-DIMM, for reduced board area and higher memory speeds.

- Support for LVTTL and SSTL-2 memory interfaces.

- Does not support SGRAM "block write" feature.

- Does not support memory interfaces less than 8MB memory configurations.

### **1.3.10** Power Management Features

- Support for version 1.0 of the ACPI Specification and version 1.1 of the PCI Bus Power Management Interface Specification (PCI PMI).

- The Chip Power Management Support logic supports four device power states On, Standby, Suspend and Off defined for the OnNow Architecture. Each power state can be achieved by software control bits.

- Clocks to every major functional block are controlled by a unique dynamic clock switching technique which is completely transparent to the software. By turning off the clock to the block that is idle or not used at that point, the power consumption is significantly reduced during normal operation.

- Self-refresh SDRAM/SGRAM in Suspend mode

- No support pin or timer mode

## **1.3.11 PC Design Guide Compliance**

M6 complies with all relevant sections of the current PC design guide specifications from Intel/Microsoft. It is fully compliant with PC99 and PC99a. It is also compliant with the current PC2001 proposal (v0.5).

## **1.3.12 Test Capability Features**

The M6 has a variety of test modes and capabilities that provide a very high fault coverage and low DPM (Defect Per Million) ratio:

- Full scan implementation on the digital core logic which provides about 99% fault coverage through ATPG (Automatic Test Pattern Generation Vectors).

- Dedicated test logic for the on-chip custom memory macros to provide complete coverage on these modules.

- A JTAG test mode (which is not entirely compliant to the IEEE 1149.1 standard) in order to allow board level testing of neighboring devices.

- An EXORTREE test mode on all the digital I/O's to allow for proper soldering verification at the board level.

- An EXTEST test mode in order to allow board level testing by sampling the inputs and controlling the outputs of M6.

- Improved access to the analog modules and PLLs in the M6 in order to allow full evaluation and characterization of these modules.

- Improved IDDQ mode support to allow chip evaluation through current leakage measurements.

These test modes can be accessed through the settings on the instruction register of JTAG circuitry.

# 1.4 Display Modes

The modes below are based on the 300MHz DAC. Some modes may not be supported in all production driver releases.

## 1.4.1 2D Display Modes

| Display              | Refresh      | Hor.          | Pixel          | Col | or Depth (b | pp) |

|----------------------|--------------|---------------|----------------|-----|-------------|-----|

| Screen<br>Resolution | Rate<br>(Hz) | Scan<br>(KHz) | Clock<br>(MHz) | 8   | 16          | 32  |

|                      | 60           | 31.5          | 25.2           | 1   | 1           | 1   |

|                      | 72           | 37.9          | 31.5           | ✓   | ✓           | 1   |

| 640x480              | 75           | 37.5          | 31.5           | ✓   | ✓           | 1   |

|                      | 85           | 43.3          | 36.0           | ✓   | ✓           | 1   |

|                      | 90           | 45.4          | 37.8           | ✓   | ✓           | 1   |

|                      | 100          | 50.9          | 43.1           | ✓   | ✓           | 1   |

|                      | 120          | 61.8          | 52.4           | 1   | 1           | 1   |

|                      | 160          | 84.3          | 72.8           | 1   | ✓           | 1   |

|                      | 200          | 108.0         | 95.0           | 1   | 1           | 1   |

#### Table 1-1 M6 2D Dispaly Modes

Preliminary

| Display              | Refresh      | Hor.          | Pixel          | Co | lor Depth (l | opp) |

|----------------------|--------------|---------------|----------------|----|--------------|------|

| Screen<br>Resolution | Rate<br>(Hz) | Scan<br>(KHz) | Clock<br>(MHz) | 8  | 16           | 32   |

|                      | 60           | 37.9          | 39.9           | ~  | ✓            | 1    |

|                      | 70           | 43.7          | 45.5           | ~  | ✓            | 1    |

|                      | 72           | 48.1          | 50.0           | ~  | ✓            | 1    |

|                      | 75           | 46.9          | 49.5           | 1  | ✓            | 1    |

| 800x600              | 85           | 53.7          | 56.3           | 1  | ✓            | 1    |

| 800x000              | 90           | 56.8          | 60.0           | 1  | ✓            | 1    |

|                      | 100          | 63.6          | 68.1           | 1  | 1            | 1    |

|                      | 120          | 77.1          | 83.9           | 1  | 1            | 1    |

|                      | 160          | 105.4         | 116.4          | 1  | 1            | 1    |

|                      | 200          | 135.0         | 149.0          | 1  | 1            | 1    |

|                      | 60           | 48.4          | 65.0           | 1  | ~            | 1    |

|                      | 70           | 56.5          | 75.0           | 1  | ~            | 1    |

|                      | 72           | 57.6          | 78.4           | 1  | ~            | 1    |

|                      | 75           | 60.0          | 78.8           | 1  | 1            | 1    |

|                      | 85           | 68.7          | 94.5           | 1  | 1            | 1    |

| 1024x768             | 90           | 72.8          | 100.1          | 1  | 1            | 1    |

| 10248766             | 100          | 81.4          | 113.3          | 1  | 1            | 1    |

|                      | 120          | 98.7          | 139.0          | 1  | 1            | 1    |

|                      | 140          | 116.6         | 164.2          | 1  | 1            | 1    |

|                      | 150          | 125.7         | 176.9          | 1  | 1            | 1    |

|                      | 160          | 134.8         | 192.0          | 1  | 1            | 1    |

|                      | 200          | 172.8         | 246.1          | 1  | 1            | *    |

Table 1-1 M6 2D Dispaly Modes (Continued)

| Display              | Refresh      | Hor.          | Pixel          | Co | or Depth (b | opp) |

|----------------------|--------------|---------------|----------------|----|-------------|------|

| Screen<br>Resolution | Rate<br>(Hz) | Scan<br>(KHz) | Clock<br>(MHz) | 8  | 16          | 32   |

|                      | 43           | 38.0          | 56.0           | 1  | 1           | 1    |

|                      | 47           | 41.7          | 62.1           | 1  | 1           | 1    |

|                      | 60           | 53.7          | 81.6           | 1  | 1           | 1    |

|                      | 70           | 63.0          | 96.7           | 1  | 1           | 1    |

|                      | 75           | 67.5          | 108.0          | 1  | 1           | 1    |

| 1152x864             | 80           | 72.4          | 112.3          | 1  | 1           | 1    |

|                      | 85           | 77.0          | 119.6          | 1  | 1           | 1    |

|                      | 100          | 91.5          | 143.4          | 1  | 1           | 1    |

|                      | 120          | 111.1         | 176.0          | 1  | 1           | 1    |

|                      | 150          | 141.4         | 226.3          | 1  | 1           | *    |

|                      | 160          | 151.6         | 242.6          | 1  | 1           | *    |

|                      | 60           | 64.0          | 108.0          | 1  | 1           | 1    |

|                      | 70           | 74.6          | 128.9          | 1  | 1           | 1    |

|                      | 74           | 79.0          | 138.5          | 1  | 1           | 1    |

| 1000-4004            | 75           | 80.0          | 135.0          | 1  | 1           | 1    |

| 1280x1024            | 85           | 91.1          | 157.5          | 1  | 1           | 1    |

|                      | 90           | 97.0          | 169.2          | 1  | 1           | 1    |

|                      | 100          | 108.5         | 190.9          | 1  | 1           | 1    |

|                      | 120          | 131.6         | 233.7          | 1  | 1           | *    |

|                      | 52           | 64.2          | 137.7          | 1  | 1           | 1    |

|                      | 58           | 71.9          | 155.4          | 1  | 1           | 1    |

|                      | 60           | 75.0          | 162.0          | 1  | 1           | 1    |

|                      | 66           | 82.2          | 178.9          | 1  | 1           | 1    |

| 1600x1200            | 75           | 93.8          | 202.5          | 1  | 1           | 1    |

|                      | 76           | 95.2          | 208.7          | 1  | 1           | 1    |

|                      | 85           | 106.3         | 229.5          | 1  | 1           | *    |

|                      | 92           | 116.4         | 257.0          | 1  | 1           | *    |

|                      | 100          | 127.1         | 280.6          | 1  | 1           | *    |

|                      | 60           | 83.5          | 203.0          | ~  | 1           | 1    |

| 1792x1344            | 75           | 105.2         | 259.3          | 1  | 1           | 1    |

|                      |              |               |                |    |             |      |

Table 1-1 M6 2D Dispaly Modes (Continued)

| Display              | Refresh      | Hor.          | Pixel          | Col | or Depth (k | opp) |

|----------------------|--------------|---------------|----------------|-----|-------------|------|

| Screen<br>Resolution | Rate<br>(Hz) | Scan<br>(KHz) | Clock<br>(MHz) | 8   | 16          | 32   |

| 1800x1440            | 60           | 89.4          | 219.5          | 1   | 1           | 1    |

| 1000x1440            | 70           | 104.9         | 249.9          | 1   | 1           | *    |

| 1856x1392            | 60           | 86.5          | 218.6          | 1   | 1           | 1    |

| 103071392            | 75           | 109.0         | 277.2          | 1   | 1           | *    |

|                      | 60           | 67.0          | 172.7          | 1   | 1           | 1    |

| 1920x1080            | 70           | 78.6          | 205.1          | 1   | 1           | 1    |

| 192021080            | 75           | 84.6          | 220.6          | 1   | 1           | 1    |

|                      | 80           | 90.4          | 237.4          | 1   | 1           | 1    |

|                      | 60           | 74.5          | 193.1          | 1   | 1           | 1    |

|                      | 72           | 90.0          | 222.2          | 1   | 1           | 1    |

| 1920x1200            | 75           | 93.9          | 231.4          | 1   | 1           | *    |

| 192021200            | 76           | 95.2          | 245.0          | 1   | 1           | *    |

|                      | 80           | 100.5         | 263.7          | 1   | 1           | *    |

|                      | 85           | 107.1         | 282.7          | 1   | 1           | *    |

| 1920x1440            | 60           | 89.4          | 234.5          | 1   | 1           | *    |

|                      | 75           | 112.7         | 297.6          | 1   | 1           | *    |

| 2049-4526            | 60           | 95.3          | 267.0          | 1   | 1           | *    |

| 2048x1536            | 70           | 111.9         | 315.2          | 1   | 1           | *    |

Table 1-1 M6 2D Dispaly Modes (Continued)

\* = Supported for all but 64 bit SDR memory as shown below

| 64-bit SDR Memory Speed | 32bpp 2D Display Support      |

|-------------------------|-------------------------------|

| 143 MHz                 | Up to 225 MHz pixel frequency |

| 167 MHz                 | Up to 265 MHz pixel frequency |

| 182 MHz                 | Up to 290 MHz pixel frequency |

| 200 MHz                 | Up to 300 MHz pixel frequency |

For 64-bit SDR memory, all display modes up to 300 MHz pixel frequency for 16bpp and 8bpp graphics are supported.

For 64-bit DDR memory, all graphics bit depths are supported for pixel frequencies up to 300 MHz. This holds for all memory speeds down to 110 MHz.

### **1.4.2 3D Modes**

| Table 1-2 3D | ) Modes |

|--------------|---------|

|--------------|---------|

| Frame<br>Buffer<br>MB | Screen<br>Resolution | Color<br>depth<br>Bit/Pixel | Front<br>Buffer<br>MB | Back<br>Buffer<br>MB | Z Buffer<br>Depth <sup>1</sup> | Z buffer<br>MB |      | Texture<br>nory <sup>2</sup><br>W/O Z<br>MB | Primary use of<br>Configuration |

|-----------------------|----------------------|-----------------------------|-----------------------|----------------------|--------------------------------|----------------|------|---------------------------------------------|---------------------------------|

| 8                     | 640x480              | 16                          | 0.59                  | 0.59                 | 16                             | 0.59           | 6.24 | 6.83                                        |                                 |

| 8                     | 640x480              | 32                          | 1.17                  | 1.17                 | 16                             | 0.59           | 5.07 | 5.66                                        |                                 |

| 8                     | 800x600              | 16                          | 0.92                  | 0.92                 | 16                             | 0.92           | 5.25 | 6.17                                        |                                 |

| 8                     | 800x600              | 32                          | 1.83                  | 1.83                 | 32                             | 1.83           | 2.51 | 4.34                                        | Value systems                   |

| 8                     | 1024x768             | 16                          | 1.50                  | 1.50                 | 32                             | 3.00           | 2.00 | 5.00                                        |                                 |

| 8                     | 1024x768             | 32                          | 3.00                  | 3.00                 | 16                             | 1.50           | 0.50 | 2.00                                        |                                 |

| 8                     | 1280x1024            | 16                          | 2.50                  | 2.50                 | 16                             | 2.50           | 0.50 | 3.00                                        |                                 |

| 16                    | 1280x1024            | 32                          | 5.00                  | 5.00                 | 32                             | 5.00           | 1.00 | 6.00                                        |                                 |

| 16                    | 1600x1200            | 16                          | 3.66                  | 3.66                 | 32                             | 7.32           | 1.35 | 8.68                                        | NA-:                            |

| 32                    | 1600x1200            | 32                          | 7.32                  | 7.32                 | 32                             | 7.32           | 10.0 | 17.35                                       | Mainstream systems              |

| 32                    | 1920x1200            | 32                          | 8.79                  | 8.79                 | 32                             | 8.79           | 5.63 | 14.42                                       |                                 |

| 64                    | 2048x1536            | 32                          | 12.0                  | 12.0                 | 32                             | 12.0           | 28.0 | 40.0                                        | PC Workstations                 |

$^1$  32 bit Z-buffer can optionally be configured as 24 bit Z-Buffer plus 8 bit Stencil Buffer.  $^2$  AGP configurations can use system memory for additional textures.

#### 1.5 **Software Features**

- Dual processor support under OpenGL driver. •

- BIOS ability to read EDID 1.1, 1.2, and 2.0.

- Ability to selectively enable and disable the panel monitor and analog monitor.

- Register-compatible with VGA standards, BIOS-compatible with VESA Super VGA. ٠

- Full Open Firmware (IEEE 1275) support. •

- Supports corporate manageability requirements such as DMI. •

- 'Instantly Available' support.

- Full Write Combining support for maximum performance on advanced processors such as Pentium III and Athlon.

- Full-featured, yet simple Windows utilities: •

- ٠ Calibration utility for WYSIWYG color

- Independent brightness control of desktop and overlay •

- End user diagnostics ٠

- SGI level III OpenGL licensee. ٠

- Drivers meet Microsoft's rigorous WHQL criteria and are suitable for systems with ٠ the "Designed for Windows NT and Windows 98" and "Designed for Windows 2000" logos.

- Comprehensive OS and API support (see table below).

- Hot-key support Mobile only.

- Extensive Power Management support. •

| Software Support               | DOS               | Win 3.x    | Win 95  | Win 98    | NT 3.51            | NT 4.0     | Windows<br>2000 | Mac OS | OS/2          |

|--------------------------------|-------------------|------------|---------|-----------|--------------------|------------|-----------------|--------|---------------|

|                                |                   |            | 2D Sof  | tware Sup | oport <sup>1</sup> |            |                 |        |               |

| Accelerated Driver             | VESA <sup>2</sup> | footnote 3 | 1       | 1         | 1                  | 1          | 1               | 1      | footnote<br>3 |

|                                |                   |            | Video S | oftware S | upport             |            |                 |        |               |

| MS DirectDraw                  |                   |            | 1       | 1         |                    | 1          | 1               |        |               |

| MS ActiveMovie/ Direct<br>Show |                   |            | 1       | 1         |                    |            | 1               |        |               |

| MPEG-1 software<br>playback    |                   |            | ~       | 1         |                    | 1          | 1               | 1      |               |

| MPEG-2 software<br>playback    |                   |            | ~       | ~         |                    |            | ~               | ~      |               |

| QuickTime<br>acceleration      |                   |            |         |           |                    |            |                 | ~      |               |

|                                |                   |            | 3D So   | ftware Su | pport              |            |                 |        |               |

| MS Direct3D                    |                   |            | 1       | 1         |                    |            | 1               |        |               |

| QuickDraw 3D RAVE              |                   |            |         |           |                    |            |                 | 1      |               |

| OpenGL                         |                   |            | ~       | 1         |                    | 1          | 1               |        |               |

| AGP                            |                   |            | ~       | 1         |                    | footnote 4 | 1               |        |               |

1 - Additional third parties (including SCO Unix and UNIXWARE)

2 - Direct BIOS support

3 - Hardware cursor only

4 - NT 4.0 Service pack 3 supports AGP devices, but does not provide support for AGP texturing

This page intentionally left blank.

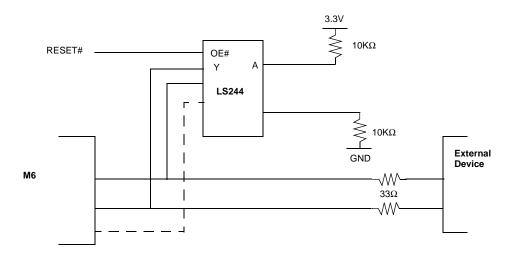

This chapter describes the signal distribution for the M6. All active low signals are shown with the suffix "#" or "*b*"(e.g., STOP#).

To link to a topic of interest, use the following list of hypertext linked cross references:

"Pin Count by Functional Group" on page 2-2 "M6 Pin Assignment Top View (Left Half)" on page 2-3 "M6 Pin Assignment Top View (Right Half)" on page 2-4 "AGP/PCI Host Bus Interface" on page 2-5 "Memory Interface (SGRAM, SDRAM)" on page 2-11 "Zoom Video Port / External TMDS Interface" on page 2-12 "General Purpose I/O Interface" on page 2-12 "LCD General Purpose I/O Interface" on page 2-12 "LVDS Interface" on page 2-13 "External SSC" on page 2-15 "Panel Control" on page 2-15 "TMDS Interface" on page 2-16 "DAC (CRT) Interface" on page 2-17 "DAC2 (TV/CRT2) Interface" on page 2-18 "Test Interface" on page 2-19 "ROM Interface" on page 2-19 "PLLs and Crystal Interface" on page 2-20 "Host Power Interface" on page 2-21 "Memory Power Interface" on page 2-21 "I/O Power Interface" on page 2-22 "Core Power Interface" on page 2-22 "Ground Interface" on page 2-22

# 2.1 Pin Count by Functional Group

The following table shows the M6 pin count listed by functional grouping.

#### Table 2-1 Pin Count

| Pin Group                  | Pin Count |

|----------------------------|-----------|

| Host Bus                   | 71        |

| Memory                     | 107+4     |

| Zoom Video / External TMDS | 28        |

| GPIO                       | 14        |

| LCD GPIO                   | 3         |

| LVDS                       | 28        |

| External SSC               | 2         |

| Panel Control              | 2         |

| TMDS / Flat Panel          | 18        |

| CRT                        | 14        |

| TV Out                     | 12        |

| Test                       | 1         |

| ROM                        | 1         |

| PLLs & XTAL                | 6         |

| Host Power                 | 19        |

| Memory I/O Power           | 19+1+10   |

| Integrated memory Power    | 8         |

| GP I/O Power               | 19        |

| Core Power                 | 24        |

| Ground                     | 74        |

| TOTAL                      | 484       |

# 2.2 Pin Assignment

## 2.2.1 M6 Pin Assignment Top View (Left Half)

|    | 1                  | 2                  | 3                  | 4                  | 5                  | 6        | 7        | 8             | 9             | 10            | 11            | 12            | 13             |

|----|--------------------|--------------------|--------------------|--------------------|--------------------|----------|----------|---------------|---------------|---------------|---------------|---------------|----------------|

| A  | VSS                | MPVDD              | MPVSS              | CLK1               | CLK1_IN            | CLK0     | CLK0_IN  | CKE           | RASb          | A(11)         | A(8)          | A(4)          | A(1)           |

| В  | DQ(32)             | VSS                | CLKFB              | CLK1b              | CLK1b_IN           | CLK0b    | CLK0b_IN | CSb(1)        | CSb(0)        | A(10)         | A(7)          | A(3)          | A(0)           |

| С  | DQ(33)             | DQ(34)             | VSS                | VSS                | VDDQM              | VDDQM    | VDDM     | CASb          | A(13)         | A(9)          | A(6)          | A(2)          | DQ(31)         |

| D  | DQ(35)             | DQ(36)             | VSS                | VSS                | VSS                | VDDQM    | VDDRH    | Web           | A(12)         | VDDM          | A(5)          | VDDM          | DQ(30)         |

| E  | DQ(37)             | DQ(38)             | VDDM               | VSS                | VSS                | VDDR1    | VDDR1    | VDDC          | VDDR1         | VDDC          | VDDR1         | VDDC          | VDDR1          |

| F  | DQ(39)             | DQMb(4)            | VDDQM              | VDDM               | VSS                |          |          |               |               |               |               |               |                |

| G  | DQMb(5)            | DQ(40)             | DQ(41)             | VDDQM              | VDDR1              |          |          |               |               |               |               |               |                |

| н  | DQ(42)             | DQ(43)             | DQ(44)             | VDDR1              | VDDC               |          |          |               |               |               |               |               |                |

| J  | DQ(45)             | DQ(46)             | DQ(47)             | QS(4)              | VDDR1              |          |          |               |               |               |               |               |                |

| к  | QS(5)              | QS(6)              | QS(7)              | VDDR1              | VDDC               |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| L  | DQ(48)             | DQ(49)             | DQ(50)             | DQ(51)             | VDDR1              |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| М  | DQ(52)             | DQ(53)             | DQ(54)             | VDDR1              | VDDC               |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| Ν  | DQ(55)             | DQMb(6)            | DQMb(7)            | DQ(56)             | VDDR1              |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| Р  | DQ(57)             | DQ(58)             | DQ(59)             | DQ(60)             | VDDR1              |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| R  | DQ(61)             | DQ(62)             | DQ(63)             | VDDR1              | VDDC               |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| т  | MEMVMO<br>DE       | VREF               | GPIO(13)           | GPIO(12)           | VDDR3              |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| U  | GPIO(11)           | GPIO(10)           | GPIO(9)            | VDDR3              | VDDC               |          |          |               |               | VSS           | VSS           | VSS           | VSS            |

| V  | GPIO(8)            | GPIO(7)            | GPIO(6)            | GPIO(5)            | VDDR3              |          |          |               |               |               |               |               |                |

| W  | GPIO(4)            | GPIO(3)            | GPIO(2)            | VDDR3              | VDDC               |          |          |               |               |               |               |               |                |

| Y  | GPIO(1)            | GPIO(0)            | ROMCSb             | ZV_LCDC<br>NTL(0)  | VDDR3              |          |          |               |               |               |               |               |                |

| AA | ZV_LCDC<br>NTL(1)  | ZV_LCDC<br>NTL(2)  | ZV_LCDC<br>NTL(3)  | ZV_LCDD<br>ATA(0)  | VDDR3              |          |          |               |               |               |               |               |                |

| AB | ZV_LCDD<br>ATA(1)  | ZV_LCDD<br>ATA(2)  | ZV_LCDD<br>ATA(3)  | ZV_LCDD<br>ATA(4)  | VDDR3              | VDDR3    | VDDC     | VDDC          | BLONb         | VDDR3         | DIGON         | VDDC          | CRT2DDC<br>CLK |

| AC | ZV_LCDD<br>ATA(5)  | ZV_LCDD<br>ATA(6)  | ZV_LCDD<br>ATA(7)  | VDDR3              | ZV_LCDD<br>ATA(23) | TESTEN   | LTGIO(2) | TXOUT_L<br>0N | TXOUT_L<br>1N | TXOUT_L<br>3N | TXOUT_U<br>1N | TXCLK_U<br>N  | LVDDR          |

| AD | ZV_LCDD<br>ATA(8)  | ZV_LCDD<br>ATA(9)  | ZV_LCDD<br>ATA(10) | ZV_LCDD<br>ATA(19) | ZV_LCDD<br>ATA(22) | LTGIO(1) | LTGIO(0) | TXOUT_L<br>0P | TXOUT_L<br>1P | TXOUT_L<br>3P | TXOUT_U<br>1P | TXCLK_U<br>P  | LVDDR          |

| AE | ZV_LCDD<br>ATA(11) | ZV_LCDD<br>ATA(12) | ZV_LCDD<br>ATA(16) | ZV_LCDD<br>ATA(18) | ZV_LCDD<br>ATA(21) | SSIN     | SSOUT    | TXOUT_L<br>2N | TXCLK_L<br>N  | TXOUT_U<br>0P | TXOUT_U<br>2P | TXOUT_U<br>3N | V2SYNC         |

| AF | ZV_LCDD<br>ATA(13) | ZV_LCDD<br>ATA(14) | ZV_LCDD<br>ATA(15) | ZV_LCDD<br>ATA(17) | ZV_LCDD<br>ATA(20) | LPVSS    | LPVDD    | TXOUT_L<br>2P | TXCLK_L<br>P  | TXOUT_U<br>0N | TXOUT_U<br>2N | TXOUT_U<br>3P | COMP_B         |

|    | 1                  | 2                  | 3                  | 4                  | 5                  | 6        | 7        | 8             | 9             | 10            | 11            | 12            | 13             |

Figure 2-1 M6 Top View (Left Half)

# 2.2.2 M6 Pin Assignment Top View (Right Half)

| 14             | 15          | 16      | 17     | 18     | 19     | 20             | 21          | 22      | 23             | 24                | 25               | 26             |    |

|----------------|-------------|---------|--------|--------|--------|----------------|-------------|---------|----------------|-------------------|------------------|----------------|----|

| DQ(29)         | DQ(25)      | DQMb(2) | DQ(20) | DQ(17) | QS(0)  | DQ(14)         | DQ(10)      | DQMb(0) | DQ(5)          | DQ(3)             | DQ(2)            | DQ(0)          | А  |

| DQ(28)         | DQ(24)      | DQ(23)  | DQ(19) | DQ(16) | QS(1)  | DQ(13)         | DQ(9)       | DQ(7)   | DQ(4)          | VDDQM             | DQ(1)            | AGPREF<br>B66  | в  |

| DQ(27)         | DQMb(3<br>) | DQ(22)  | DQ(18) | QS(3)  | DQ(15) | DQ(12)         | DQ(8)       | DQ(6)   | VDDM           | VDDQM             | AGPTEST          | AD(1)<br>B65   | с  |

| DQ(26)         | VDDQM       | DQ(21)  | VDDM   | QS(2)  | VDDQM  | DQ(11)         | DQMb(1<br>) | VDDQM   | VDDM           | AD(0)<br>A65      | AD(2)<br>A63     | AD(3)<br>B63   | D  |

| VDDR1          | VDDC        | VDDR1   | VDDC   | VDDR1  | VDDC   | VDDR1          | VDDR1       | VDDP    | AD(4)<br>A62   | AD(6)<br>A60      | AD(5)<br>B62     | AD(7)<br>B60   | E  |

|                |             |         |        |        |        |                |             | VDDP    | CBEb(0)        | AD_STBb(0)        | AD_STB(0)<br>B59 | AD(8)<br>B57   | F  |

|                |             |         |        |        |        |                |             | VDDP    | AD(9)<br>A56   | AD(11)<br>A54     | AD(10)<br>B56    | AD(12)<br>B54  | G  |

|                |             |         |        |        |        |                |             | VDDC    | VDDP           | AD(13)<br>A53     | AD(15)<br>A51    | AD(14)<br>B53  | н  |

|                |             |         |        |        |        |                |             | VDDP    | PAR<br>A50     | STOPb<br>A47      | CBEb(1)<br>B51   | DEVSELb<br>B46 | J  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDC    | VDDP           | TRDYb<br>A46      | FRAMEb<br>A41    | IRDYb<br>B41   | к  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDP    | AD(16)<br>A39  | AD(18)<br>A38     | CBEb(2)<br>B39   | AD(17)<br>B38  | L  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDC    | VDDP           | AD(20)<br>A36     | AD(22)<br>A35    | AD(19)<br>B36  | м  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDP    | CBEb(3)<br>A33 | AD_STBb(1)<br>A32 | AD(21)<br>B35    | AD(23)<br>B33  | N  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDP    | AD(24)<br>A30  | AD(26)<br>A29     | AD_STB(1)<br>B32 | AD(25)<br>B30  | Р  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDC    | VDDP           | AD(28)<br>A27     | AD(27)<br>B29    | AD(29)<br>B27  | R  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDP    | AD(30)<br>A26  | SBA(7)<br>A21     | AD(31)<br>B26    | SBA(6)<br>B21  | т  |

| VSS            | VSS         | VSS     | VSS    |        |        |                |             | VDDC    | VDDP           | SBA(5)<br>A20     | SB_STBb<br>A18   | SBA(4)<br>B20  | U  |

|                |             |         |        |        |        |                |             | VDDP    | SBA(3)<br>A17  | SBA(1)<br>A15     | SB_STB<br>B18    | SBA(2)<br>B17  | v  |

|                |             |         |        |        |        |                |             | VDDC    | VDDP           | SERRb<br>A14      | SBA(0)<br>B15    | RBFb<br>B12    | w  |

|                |             |         |        |        |        |                |             | VDDP    | ST(1)<br>A10   | GNTb<br>A8        | ST(2)<br>B11     | ST(0)<br>B10   | Y  |

|                |             |         |        |        |        |                |             | VDDP    | RSTb<br>A7     | INTAb<br>A6       | REQb<br>B8       | PCICLK<br>B7   | AA |

| VDDC           | VDDR3       | VDDR3   | VDDC   | VDDR3  | VDDC   | VDDR3          | VDDR3       | VDDR3   | VDDP           | VDDP              | STP_AGPb         | AGP_BUSYb      | AB |

| CRT2DD<br>CDAT | A2VSSN      | A2VSSN  | VDDR3  | TXVSSR | TXVDDR | DVIDDC<br>DATA | AVSSQ       | AUXWIN  | VDDR3          | VDDR3             | VGADDCCLK        | VGADDCDATA     | AC |

| H2SYNC         | A2VSSQ      | A2VDDQ  | A2VDD  | TXVSSR | TXVDDR | DVIDDC<br>CLK  | HPD         | AVSSN   | AVDD           | MONID(0)          | MONID(1)         | PVSS           | AD |

| LVSSR          | LVSSR       | R2SET   | TXVSSR | ТХСМ   | TX0M   | TX1M           | TX2M        | RSET    | VSYNC          | HSYNC             | SUS_STATb        | PVDD           | AE |

| Y_G            | C_R         | TPVSS   | TPVDD  | TXCP   | TX0P   | TX1P           | TX2P        | В       | G              | R                 | XTALIN           | XTALOUT        | AF |

| 14             | 15          | 16      | 17     | 18     | 19     | 20             | 21          | 22      | 23             | 24                | 25               | 26             |    |

| Figure 2-2 | M6 Top View | (Right Half) |

|------------|-------------|--------------|

|------------|-------------|--------------|

# 2.3 AGP/PCI Host Bus Interface

| Pin Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTb 1     | I    | Active Low PCI Reset,<br>All PCI signals on the M6 will be tri-stated during its assertion This<br>signal may be asserted or de-asserted asynchronously to the PCICLK,<br>but it must be guaranteed to be clean and have bounce-free edges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PCICLK     | 1    | Bus Clock,<br>this signal is used as a reference for all transactions on the PCI bus.<br>Except for RSTb and INTAb, all PCI signals are sampled on the rising<br>edge of this clock signal and all timing parameters are defined with<br>respect to this rising edge. It's frequency can be 33 - 66 Mhz<br>depending on the system bus type (PCI 33 - PCI 66 - AGP)                                                                                                                                                                                                                                                                                                                                                                                                         |

| AD(31:0)   | I/O  | Address/Data (31:0)<br>A bus cycle consists of an address phase followed by one or more<br>data phases.<br><b>PCI</b> : when the M6 is a target on the PCI bus, these signals are inputs<br>for address read/writes and write data, and outputs for read data.<br>This bus contains the address during the clock cycle in which<br>FRAMEb is asserted (address phase), and it contains the data in the<br>subsequent clock cycles.<br><b>AGP</b> : the M6 acts as an AGP master. Data is driven or received<br>through the AD lines by the M6 after appropriate commands are sent<br>to the host-to-PCI bridge via the side band address bus (SBA(7:0))<br>Note: in AGP mode, AD16 or AD17 (depending on the IDSELb strap<br>setting) are also used for the IDSEL function. |

| C/BEb(3:0) | I/O  | Bus Command/ Byte Enable(3:0)<br><b>PCI</b> : during the address phase of a transaction, these signals define<br>the bus command (Int ack., spec. cycle, IO R/W, Mem R/W, Config<br>R/W, etc.).<br>During the data phase, they are used as Byte Enables (determine<br>which byte on the AD line carries meaningful data)<br><b>AGP</b> : provide valid byte information during AGP write transactions<br>and are driven by the master. They are driven to ë0000í by the target<br>and ignored by the master (M6) during the return of AGP read data.                                                                                                                                                                                                                        |

| FRAMEb     | I/O  | Cycle Frame<br><b>PCI</b> : this signal is driven by the current master to indicate the<br>beginning and duration of an access. It is asserted to indicate the<br>beginning of a bus transaction. Data transfer will continue while this<br>signal is asserted. When FRAMEb is deasserted, the transaction is in<br>its final data phase.<br><b>AGP</b> : not used in AGP and kept in its deasserted state                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 2-2 AGP/PCI Host Bus Interface

|          | Turner | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IRDYb    | I/O    | Initiator (bus master) ready<br><b>PCI</b> : it indicates the ability of the current initiator (current bus master)<br>to complete the current data phase of the transaction.<br>During a write cycle, IRDYb indicates that valid data is present on the<br>AD line.<br>During a read cycle, it indicates that the master is ready to accept<br>data.<br>IRDYb is used in conjunction with the TRDYb signal.<br>Wait cycles are inserted until both IRDYb and TRDYb are asserted.<br>A data phase is completed on any clock where both IRDYb and<br>TRDYb are sampled as asserted.<br><b>AGP</b> : for AGP writes, it indicates that the master is ready to provide<br>all write data for the current write transaction. Once this signal is<br>asserted for a write operation, the master is not allowed to insert wait<br>states.<br>For AGP reads, the assertion of this signal indicates that the master is<br>ready to accept a subsequent block (32 bytes) of read data. the<br>master is never allowed to insert a wait state during the initial block of<br>a read transaction, but it may do so after subsequent block transfers.<br>(there is no FRAMEb IRDYb relationship for AGP transactions)<br>The target is allowed to insert wait states on block boundaries but not<br>on individual data phases (for both Read and Write operations) |

| TRDYb    | I/O    | Target device ready<br><b>PCI</b> : it indicates the ability of the target to complete the current data<br>phase of the transaction<br>During a read cycle, TRDYb indicate that valid data is present on the<br>AD line.<br>During a write cycle, it indicates that the target is ready to accept data.<br>TRDYb is used in conjunction with IRDYb.<br>Wait cycles are inserted until both IRDYb and TRDYb are asserted.<br>A data phase is completed on any clock where both IRDYb and<br>TRDYb are sampled as asserted.<br><b>AGP</b> : for AGP reads, it indicates that the target is ready to provide<br>read data for the entire transaction (when transaction can complete<br>within four clocks) or is ready to transfer a (initial or subsequent) block<br>of data when the transfer requires more than four clocks to complete.<br>The target is allowed to insert wait states after each block transfers on<br>both read and write transaction                                                                                                                                                                                                                                                                                                                                                                                                |

| DEVSELb  | I/O    | Device select<br><b>PCI</b> : when actively driven, it indicates that the driving device (target)<br>has decoded its address as the target of the current access.<br>As an input to other devices and the current master, it indicates<br>whether any device on the bus has been selected.<br><b>AGP</b> : not used in AGP and kept in its deasserted state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |