# *CL-GD7556*

## **OVERVIEW**

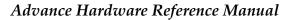

The CL-GD7556 is the second product in a new family of 64-bit GUI and video-accelerated LCD/CRT controllers. It supports all of the highest operating modes of the CL-GD7555, but it does it at 3.3 V to save operating power. It offers 64-bit graphics performance and superb video quality with its trend-setting video-color adjustment, MVA features, and scaling engine. With on-chip video-acceleration features and V-Port<sup>™</sup> support, the CL-GD7556 is an extremely flexible and cost-effective multimedia solution for premium portable computer designs. The CL-GD7556 surpasses desktop-system equivalency by providing 'desktop-replacement' performance, features, and display mode support for the office.

## FEATURES

- True 64-bit acceleration

- 64-bit BitBLT acceleration engine

- 64-bit display memory interface

- 64-bit data paths

#### ■ GUI acceleration

- BitBLT setup register double buffering with autostart

- Transparent BitBLT (source color key)

- Memory-mapped I/O

- True packed-pixel addressing for 8, 16, and 24 bpp

#### Direct-connect 32-bit PCI v2.1 host bus interface

- Multiple apertures to support simultaneous high-performance graphics and video

- Extended burst cycle and automatic bus retry support for high data transfer rates

## Low-Power, High-Performance 64-Bit Video- and Graphics-Accelerated LCD/CRT Controller

#### Enhanced video acceleration

- X and Y interpolated scaling engine

- EST (edge-sharpening technology) option with upscaling

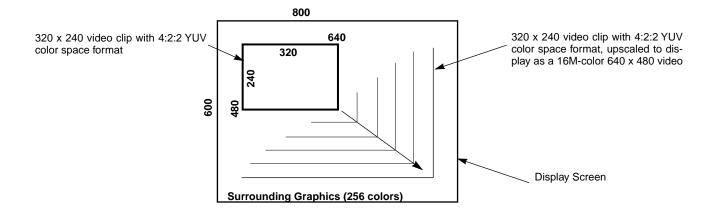

- Continuous video upscaling to  $1024 \times 768$

- Easy, independent end-user control of color, brightness, and contrast of the video window to compensate for the various color characteristics of the display and media

- DirectDraw<sup>™</sup>/DirectVideo<sup>™</sup> (Windows<sup>®</sup> 95) and DCI1.X (display control interface for Windows<sup>®</sup> 3.X) support for full-motion video playback acceleration

- Integrated color space converter for 4:2:2 YCrCb to RGB 8:8:8

- Hardware destination color- and chroma-key support (hardware occlusion)

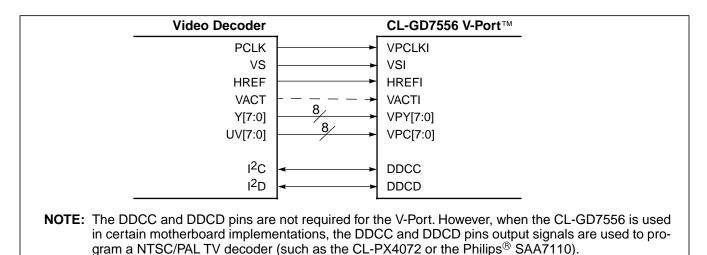

- V-Port<sup>™</sup> and VPM (video port manager) support for PC Card ZV-Port specification

- Acceleration of MPEG-1, True Motion<sup>™</sup>, CinePak<sup>™</sup>, and Indeo<sup>™</sup> software-coded video

- Video format support for 24- and 16-bpp RGB, 4:2:2 YCrCb, and proprietary compressed formats — AccuPak™ and DYUV 8-bpp YCrCb

#### Scalable, high-performance memory interface

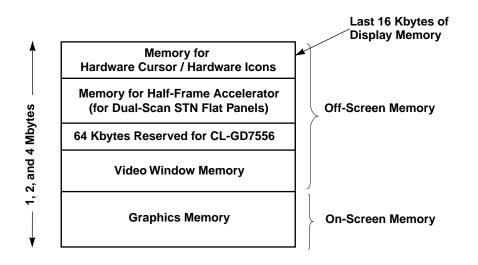

- 64-bit interface supporting 1, 2, and 4 Mbytes

- Optimized for EDO (extended-data-out) DRAM

- Single design can support 2-Mbyte (four 256K × 16) and 1-Mbyte (four 128K × 16) memory configurations

## FEATURES (cont.)

### Portable-Specific Features

#### ■ Display device support

- TFT:  $1024 \times 768$ ,  $800 \times 600$ ,  $640 \times 480$

- DSTN: 1024 × 768, 800 × 600, 640 × 480

- CRT: 1280 × 1024, 1024 × 768, 800 × 600, 640 × 480

- NTSC and PAL TV through analog encoder

#### ■ Flat panel-specific support

#### - Color TFT flat panels:

- 1-pixel/shift clock (9-, 12-, 18-, and 24-bit interfaces); 2-pixel/shift clock (18-bit direct-connect interface)

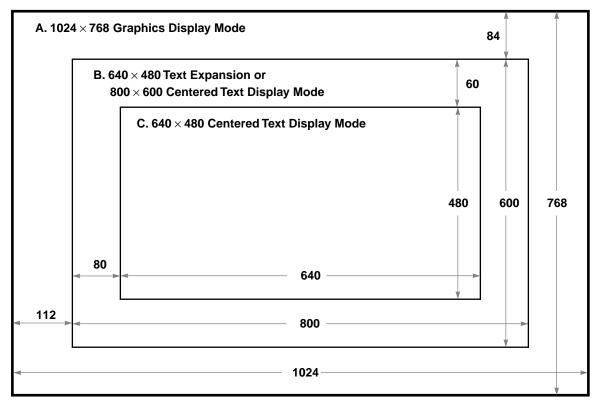

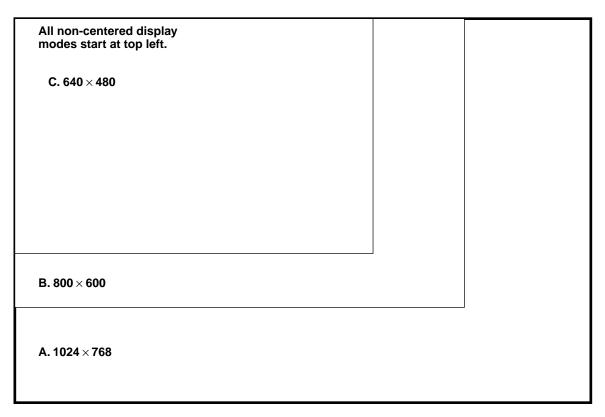

- Enhanced hardware expansion of lower-resolution VGA display modes up to 800 × 600 on higher-resolution flat panels

- Automatic centering of lower-resolution VGA display modes on higher-resolution flat panels

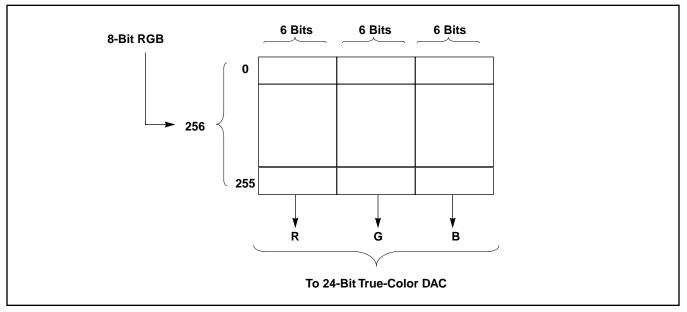

- Dithering algorithm automatically adds up to 8 bits per primary color without decreasing resolution

- Enhanced frame-rate modulation algorithm improves display quality with fast-response DSTN flat panels

#### Integration

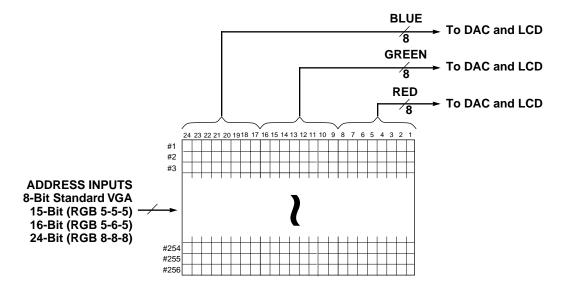

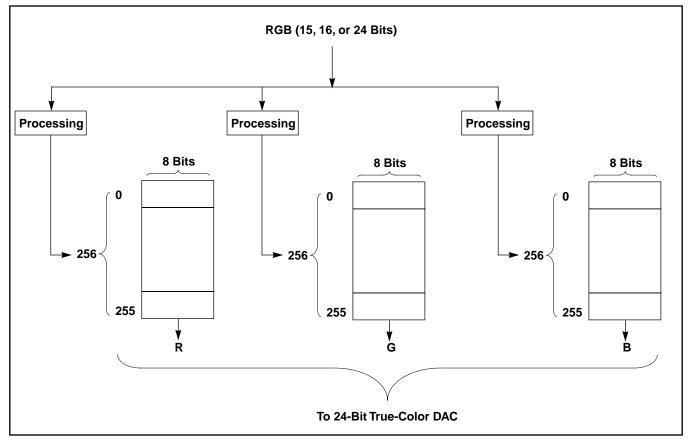

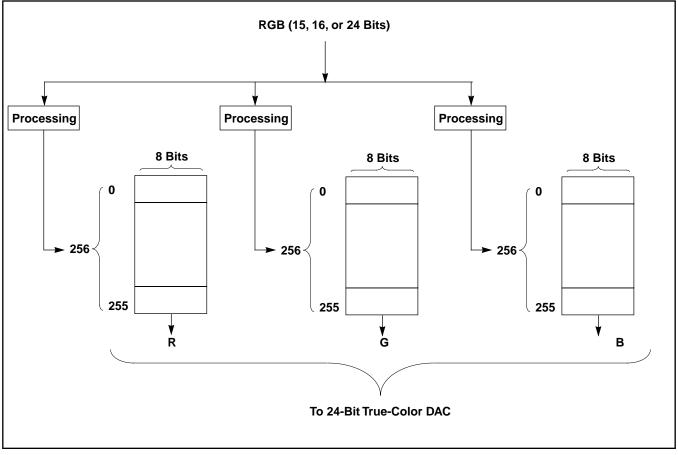

- 24-bit true-color palette and DAC with support for gamma/color adjustment in High- and True-Color modes

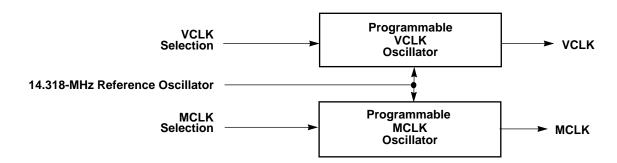

- Programmable frequency synthesizer: up to 80-MHz MCLK at 3.3 V; up to 135-MHz VCLK at 3.3 V

#### Power-management capabilities

- Low operating power, since all modes supported at 3.3 V

- All 3.3-V I/O pins can interface to 5.0-V TTL logic

- Active power management provides power-down control of select unused internal functional blocks during display

- Suspend and Standby mode support

- VESA<sup>®</sup> DPMS (display power management signaling) support

- DDC-2B (display data channel) support

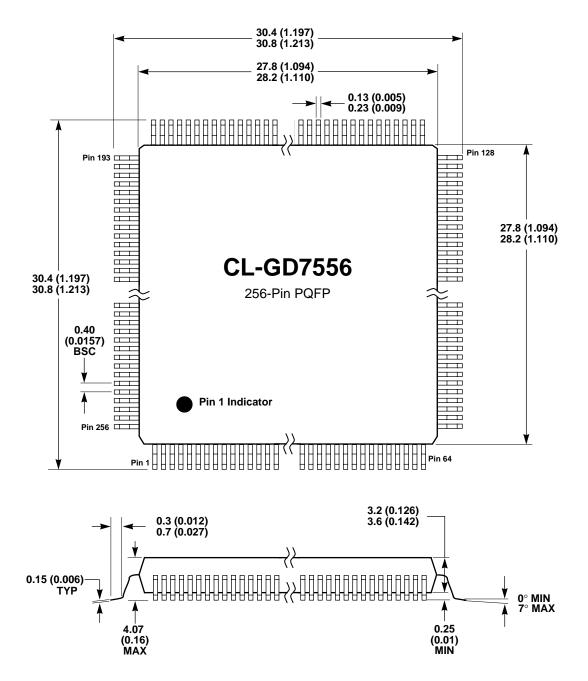

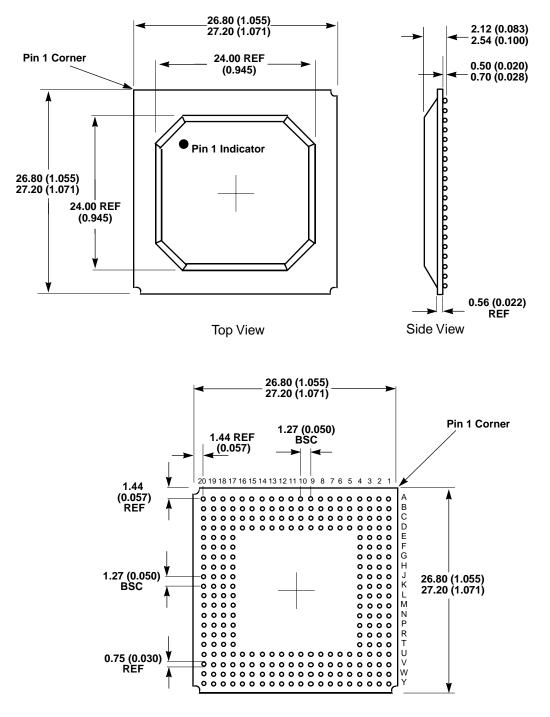

- Packaging

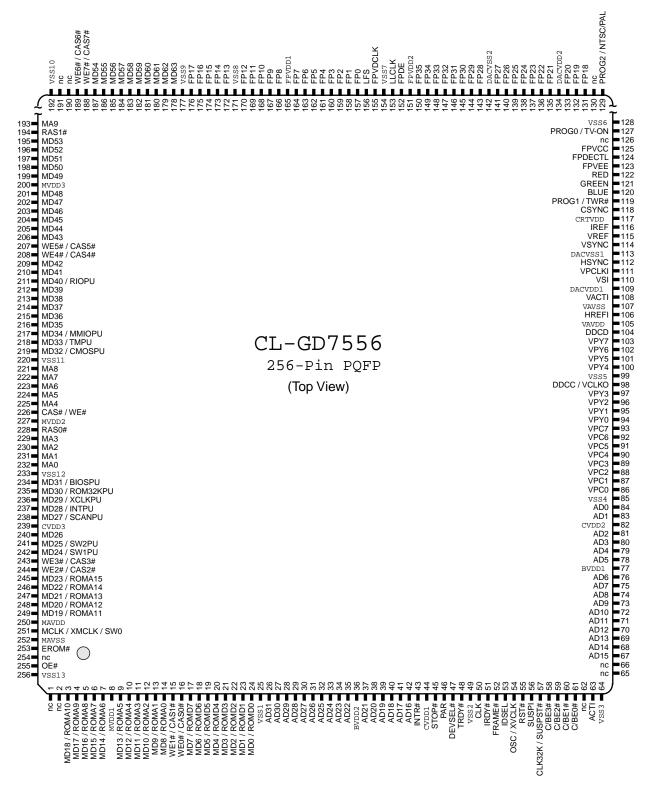

- 256-pin PBGA (plastic ball grid array) 27 mm  $\times$  27 mm

- 256-pin PQFP (plastic quad flat pack) 28 mm × 28 mm

## **PRODUCT DESCRIPTION**

The outstanding GUI performance of the CL-GD7556 is accomplished with 64-bit architecture (64-bit BitBLT engine, memory interface, and data paths), and an ability to effectively eliminate setup latency during BitBLT operations by double-buffering BitBLT setup registers. In addition, optimizing support for the burst capabilities of PCI v2.1 (with multiple apertures, extended burst cycle support, auto bus retry, and a properly sized write buffer) boosts CL-GD7556 performance in all environments.

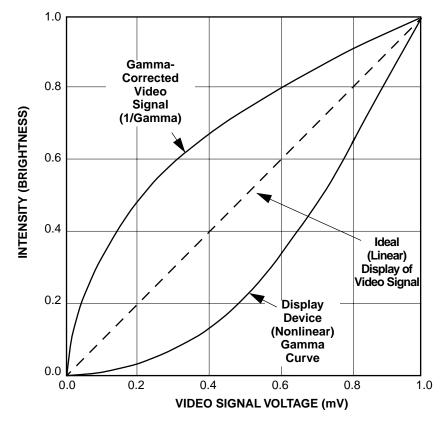

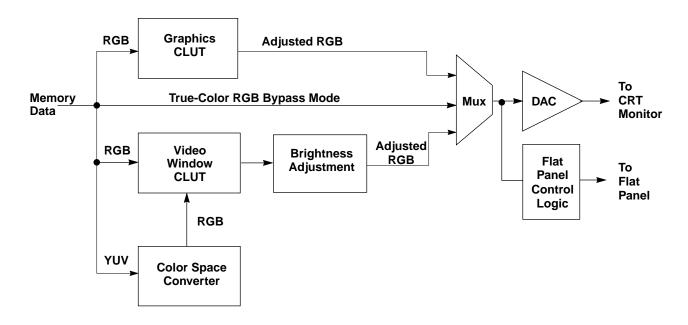

With its MVA (MotionVideo<sup>™</sup> Acceleration) features, the CL-GD7556 leads the industry in multimedia video quality. In addition, the CL-GD7556 provides graphics color/brightness correction and a powerful scaling engine with EST (edge-sharpening technology). The color/brightness adjustment allows the CL-GD7556 to compensate for color and brightness variations of display devices (for example, TFT, DSTN, CRT, TV), resulting in consistent image display on various display devices and from various sources.

The CL-GD7556 also allows separate end-user color and brightness adjustment of the video window, independent of the overall display (the first portable graphics controller to offer this feature). This adjustment is important because almost all recorded video (including video recorded by camcorders) is gamma pre-corrected for a TV display. The end user can adjust the color and brightness of the video window in much the same way as it can be adjusted on a color TV. The end user can compensate for both the characteristics of the specific display device to be used and for

loss of color fidelity caused by video recording, compression, and decompression.

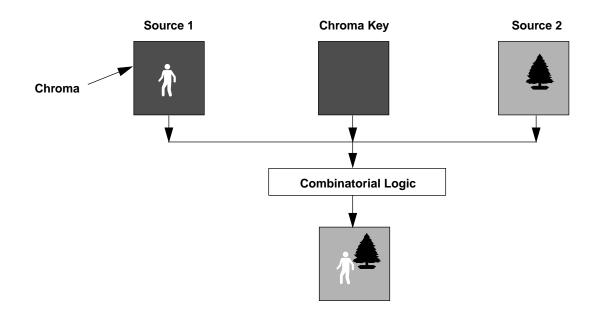

To support multimedia special effects, the CL-GD7556 provides hardware occlusion (destination color/chroma keying) and transparent BitBLT (source color/chroma keying). Windows<sup>®</sup> 95 and DirectDraw<sup>™</sup> emulate these functions in software; however, DirectDraw can recognize and use hardware support for these operations, greatly accelerating them.

The CL-GD7556 also offers flexibility for implementation. V-Port support allows cost-effective implementation of many multimedia features (MPEG video playback, TV tuner, video capture, and teleconferencing). These V-Port–related functions can be implemented on the motherboard or added later as ZV-Port–enabled PC Cards.

In most high-end implementations, the CL-GD7556 is likely to be implemented with a 2-Mbyte frame buffer using four 256K  $\times$  16 DRAMs. However, a more cost-effective mid-range 1-Mbyte product can be implemented using the same board design and replacing the four 256K  $\times$  16 DRAMs with four pin-compatible 128K  $\times$  16 DRAMs. The graphics benchmark performance of the 1-Mbyte configuration is the same, but fewer modes are supported.

To summarize, the CL-GD7556 is an industry-leading portable graphics solution with exceptional graphics performance and superb video quality, allowing much flexibility in implementation.

ii

| FEATURES                                                                                                                  | CL-GD7556                   | _ | BENEFITS                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Performance                                                                                                               | 1                           |   |                                                                                                                                                                                              |

| <ul> <li>Winmark<sup>®</sup> 95 expectation (Pentium<sup>®</sup><br/>166, Windows<sup>®</sup> 95, Winbench 96)</li> </ul> | >30M Winmarks               |   | Better end-user responsiveness.                                                                                                                                                              |

| BitBLT engine                                                                                                             | Second-generation<br>64-bit |   | Proven core design and driver base.                                                                                                                                                          |

| Transparent BitBLT                                                                                                        | 1                           |   | Enhances Windows <sup>®</sup> 95 game performance; enables non-rectangular<br>BitBLTs.                                                                                                       |

| Memory-mapped I/O                                                                                                         | 1                           |   | Improves performance by reducing host CPU cycles.                                                                                                                                            |

| <ul> <li>Double-Buffer BitBLT registers<br/>(BitBLAST)</li> </ul>                                                         | 1                           |   | Allows one BitBLT register to be set up while another BitBLT register is executing; eliminates BitBLT setup latency.                                                                         |

| Optimized PCI host interface                                                                                              | PCI v2.1; 33 MHz            |   | High-performance industry-standard interface.                                                                                                                                                |

| PCI bus retry                                                                                                             | <i>✓</i>                    |   | Automatically monitors the bus for an opening to transmit multimedia data.                                                                                                                   |

| Multiple PCI apertures                                                                                                    | 1                           |   | Accelerates PCI bus master video transfers. Dedicated aperture for multimedia use, while other apertures service normal PCI traffic.                                                         |

| Optimized write buffer                                                                                                    | 32-bit × 8-level-deep       |   | Sized to optimize PCI burst bandwidth.                                                                                                                                                       |

| Burst support                                                                                                             | 1                           |   | Significantly enhances PCI bandwidth.                                                                                                                                                        |

| ■ Proprietary FasText <sup>™</sup> text acceleratio                                                                       | n 🗸                         |   | Maintains true VGA compatibility (two fonts in plane 2).<br>Enables high refresh rate in text display modes with $800 \times 600$ DSTN flat panels.                                          |

| Multimedia Video                                                                                                          |                             |   |                                                                                                                                                                                              |

| ZV-Port (V-Port™)                                                                                                         | ✓                           |   | Allows flexible after-market multimedia upgrade of portable PCs.                                                                                                                             |

|                                                                                                                           |                             |   | Off-loads video bandwidth from the PCI bus, which improves system performance.                                                                                                               |

| <ul> <li>Independent color adjustment of<br/>graphics display and video window;</li> </ul>                                | <ul> <li>✓</li> </ul>       | ٦ | Normalizes color fidelity between vendor's flat panels and other display device types.                                                                                                       |

| independent brightness control of vide<br>window                                                                          | 20                          |   | Allows end user to adjust color and brightness to their preference in the video window and the graphics background.                                                                          |

| <ul> <li>Hardware source (transparent BitBLT<br/>and destination (occlusion) color and</li> </ul>                         | ) 🗸                         |   | Allows video data to maintain frame data rate when video window is occluded by graphics data.                                                                                                |

| chroma key support to $1024 \times 768$                                                                                   |                             |   | Required to accelerate video in Windows <sup>®</sup> 95 games.                                                                                                                               |

|                                                                                                                           |                             |   | Source and destination color and chroma key support complies with DirectDraw <sup>™</sup> specification.                                                                                     |

| Continuous X and Y interpolated scalir to $1024 \times 768$ , scaling option to use                                       | ng 🗸                        |   | Smooth upscaling of video up to $1024 \times 768$ while reducing image aliasing (that is, blockiness of image).                                                                              |

| algorithm that maintains edge sharpness during upscaling                                                                  |                             |   | Reduces host CPU bandwidth by off-loading scaling function to<br>graphics controller.                                                                                                        |

|                                                                                                                           |                             |   | Greatly reduces PCI and memory bandwidth by transferring video in its native resolution ( $352 \times 240$ rather than $1024 \times 768$ ).                                                  |

| Color space conversion                                                                                                    | 1                           |   | Converts 16-bpp YUV to 24-bpp true-color RGB.                                                                                                                                                |

|                                                                                                                           |                             |   | Converts compressed 8-bpp AccuPak™ or DYUV to high-color RGB.                                                                                                                                |

|                                                                                                                           |                             |   | Frees host CPU, PCI, and memory bandwidth, which would otherwise<br>be required for color space conversion.                                                                                  |

| <ul> <li>Frame buffer support for mixed forma<br/>and color depth</li> </ul>                                              | ts 🗸                        |   | RGB, YUV, AccuPak™, and compressed YUV can coexist in the frame<br>buffer — important because YUV, AccuPak™, and compressed YUV<br>are more efficient formats for memory size and bandwidth. |

|                                                                                                                           |                             |   | Allows the color depth of video to be independent of background<br>graphics color depth, reducing memory and bandwidth requirements<br>for quality video.                                    |

## SOFTWARE SUPPORT

#### **Operating System and Application Software Drivers**

| Software Drivers <sup>a</sup>                                                                                                          | Resolution Supported |                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microsoft <sup>®</sup> Windows <sup>®</sup> v3.X                                                                                       | CRT Only             | $640 \times 480, 800 \times 600, 1024 \times 768, 1280 \times 1024$                                                                                         |

| Microsoft <sup>®</sup> Windows <sup>®</sup> 95                                                                                         | SimulSCAN™           | 640 × 480, 800 × 600, 1024 × 768                                                                                                                            |

| Microsoft <sup>®</sup> /Intel <sup>®</sup> DCI™                                                                                        | SimulSCAN            | 640 × 480, 800 × 600, 1024 × 768                                                                                                                            |

| DirectDraw <sup>™</sup> /DirectVideo <sup>™</sup> for Windows <sup>®</sup> 95<br>Includes low-resolution support for game applications | SimulSCAN            | $\begin{array}{c} 320 \times 200, \ 320 \times 240, \ 512 \times 384, \ 640 \times 400, \\ 640 \times 480, \ 800 \times 600, \ 1024 \times 768 \end{array}$ |

| Cirrus Logic VPM (video port manager) for ZV-Port<br>and V-Port™ solutions                                                             | SimulSCAN            | 640 × 480, 800 × 600, 1024 × 768                                                                                                                            |

| Microsoft <sup>®</sup> Windows NT™ v3.5X, 4.0                                                                                          | SimulSCAN            | 640 × 480, 800 × 600, 1024 × 768                                                                                                                            |

| OS/2 <sup>®</sup> , WARP 4.0                                                                                                           | CRT Only             | $640 \times 480, 800 \times 600, 1024 \times 768, 1280 \times 1024$                                                                                         |

| 03/2 , WARF 4.0                                                                                                                        | SimulSCAN            | 640 × 480, 800 × 600, 1024 × 768                                                                                                                            |

| AutoCAD <sup>®</sup> v11, v12, Autoshade <sup>®</sup> v2.0,                                                                            | CRT Only             | $640 \times 480, 800 \times 600, 1024 \times 768, 1280 \times 1024$                                                                                         |

| 3D Studio <sup>®</sup> v1, v2                                                                                                          | SimulSCAN            | 640 × 480, 800 × 600, 1024 × 768                                                                                                                            |

<sup>a</sup> Driver support for additional applications is provided by independent software vendors, either with specific drivers or through VESA<sup>®</sup> mode support. For more information concerning driver support, contact the software manufacturer.

#### BIOS

| Feature                                                                           | Benefit                                                                                                                                     |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 48-Kbyte VGA BIOS                                                                 | □ Provides optimum performance with VGA and VESA <sup>®</sup> extended display mode support.                                                |

|                                                                                   | Provides system design options for the best combination of performance and functionality.                                                   |

| ■ Fully IBM <sup>®</sup> -compatible VGA BIOS                                     | Compatible with the existing base of PC applications.                                                                                       |

| VESA <sup>®</sup> VBE (VGA BIOS extensions)<br>v1.2, DDC-2B, and power management | Compatible with industry standards for extended display mode support beyond VGA, intelligent monitor sensing, and power-management control. |

#### Software Utilities

| Utility                                                   | Function                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           | Windows <sup>®</sup> 3.X and DOS utilities (available in various foreign-language transla-<br>tions) for configuration of graphics display modes and display device type.                                                                                          |

| WinMode and CLMode                                        | Windows <sup>®</sup> 95 utilities (available in various foreign-language translations.)<br>– Refresh rate selection<br>– Display device selection                                                                                                                  |

| OEMSI                                                     | VGA BIOS-customization utility for OEM development use.                                                                                                                                                                                                            |

| PCLRegs                                                   | DOS-based VGA register viewer/editor for OEM development use.                                                                                                                                                                                                      |

| V-Port™ Regs                                              | Windows <sup>®</sup> -based VGA register viewer/editor and V-Port™/video window display-con-<br>figuration utility for OEM development use.                                                                                                                        |

| Color balance utility for color and brightness adjustment | End-user utility allowing color and brightness adjustments of both the graphics CLUT and the video-window CLUT to compensate for both the color/brightness variations of the display device, and any color fidelity variations in the video media being displayed. |

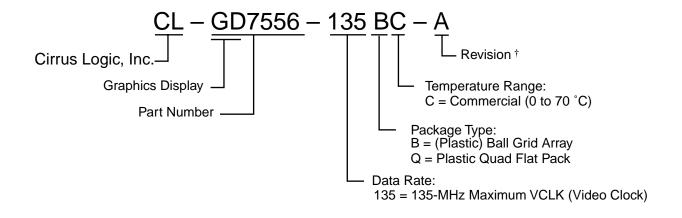

Ordering Part Number:

iv

CL-GD7556 - 135BC

Where:

B = Ball-Grid Array Package

C = Commercial Temp. ( $0^{\circ}$ C to  $70^{\circ}$ C)

## TABLE OF CONTENTS

|            | PRODUCT DESCRIPTION                                                                         | ii   |

|------------|---------------------------------------------------------------------------------------------|------|

|            | TABLE OF CONTENTS                                                                           | 1    |

|            | CONVENTIONS AND TRADEMARKS                                                                  |      |

| 1.         | PIN INFORMATION                                                                             |      |

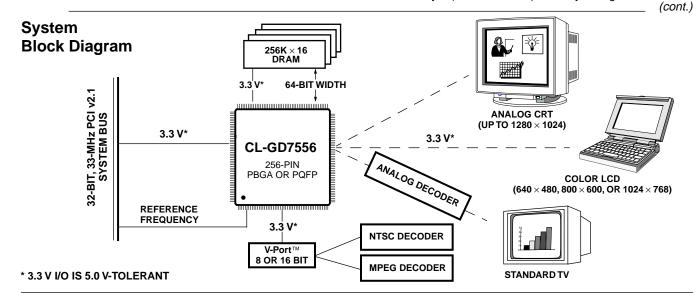

| 1.1        | Pin Diagram of Plastic Quad Flat Package                                                    |      |

| 1.2        | Pin Diagram of Plastic Ball Grid Array                                                      |      |

| 1.3        | Pin Tables                                                                                  | 1-3  |

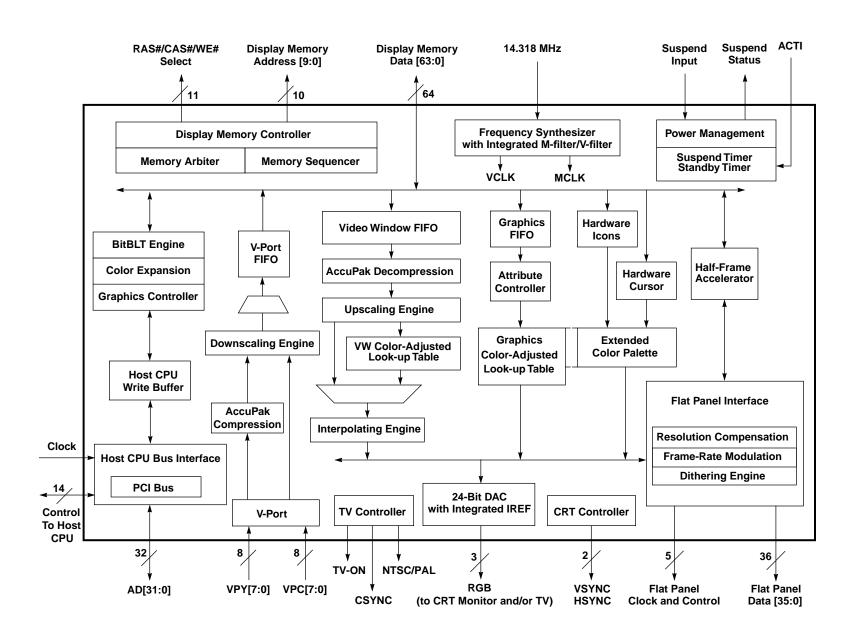

| 1.4        | Block Diagrams: CL-GD7556 Interfaces to PCI Bus                                             | 1-10 |

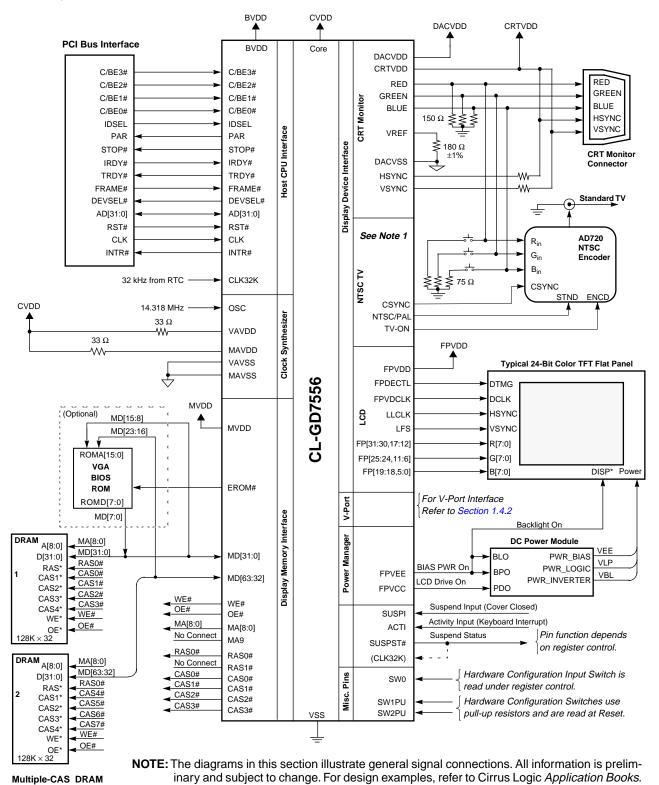

| 1.4.1      | 1-Mbyte 128K $	imes$ 32 DRAM, 24-Bit, 640 $	imes$ 480 Color TFT                             | 1-10 |

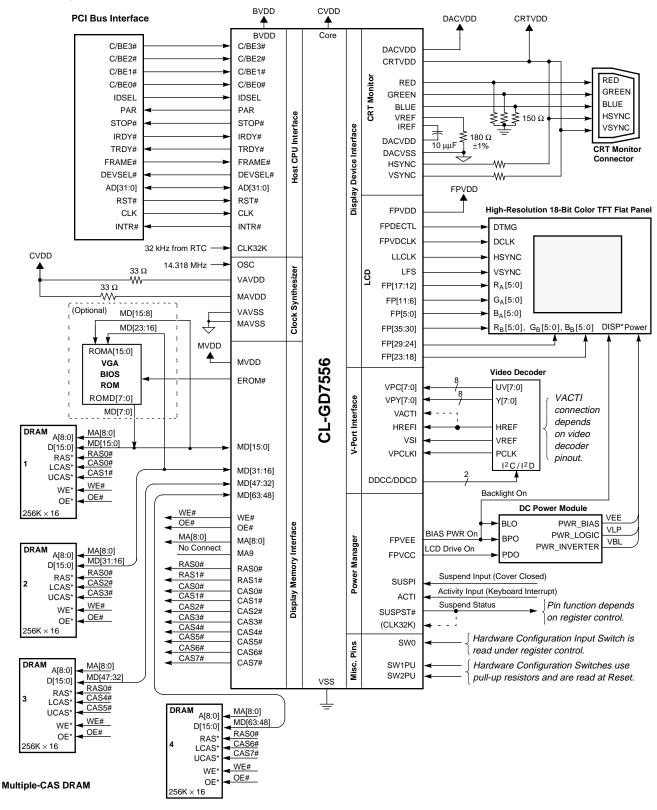

| 1.4.2      | 2-Mbyte 256K $\times$ 16 DRAM, 18-Bit Color TFT with 2-Pixels/Clock                         | 1-11 |

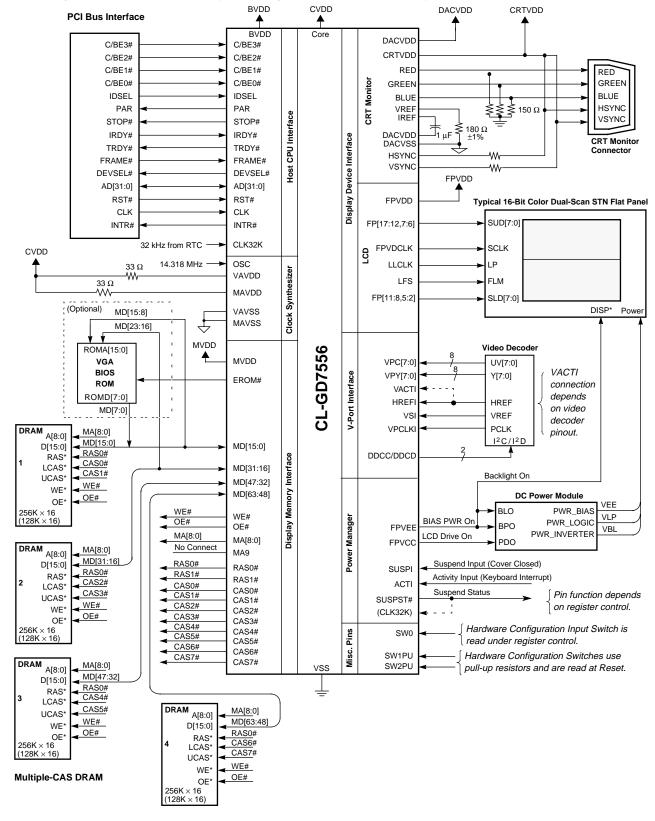

| 1.4.3      | 2-Mbyte 256K $\times$ 16 DRAM (or 1-Mbyte 128K $\times$ 16 DRAM), 800 x 600 Color Dual-Scan | 1-12 |

| 2.         | PIN DESCRIPTIONS                                                                            |      |

| 2.1        | PCI Bus Interface                                                                           |      |

| 2.2        | Flat Panel Interface and Control Pins                                                       |      |

| 2.2.1      | TFT Flat Panel Interface Pins                                                               |      |

| 2.2.2      | Dual-Scan STN Flat Panel Interface Pins                                                     |      |

| 2.2.3      | Flat Panel Control Pins                                                                     |      |

| 2.3        | CRT Monitor Interface Pins                                                                  |      |

| 2.4        | NTSC and PAL TV Interface Pins                                                              |      |

| 2.5        | Dual-Frequency Synthesizer Interface Pins.                                                  |      |

| 2.6        | Display Memory Interface Pins                                                               |      |

| 2.7<br>2.8 | V-Port Interface Pins<br>Configuration Input Pins                                           |      |

| 2.0        | On-Chip PCI VGA BIOS Support Pins                                                           |      |

| 2.10       | Programmable-Output, Switch, and Test Mode Pins                                             |      |

| 2.11       | Power-Management Pins                                                                       |      |

| 2.12       | Ground Pins                                                                                 |      |

| 2.13       | Power Pins                                                                                  |      |

| 3.         | FUNCTIONAL DESCRIPTION                                                                      | 3-1  |

| 3.1        | Introduction                                                                                |      |

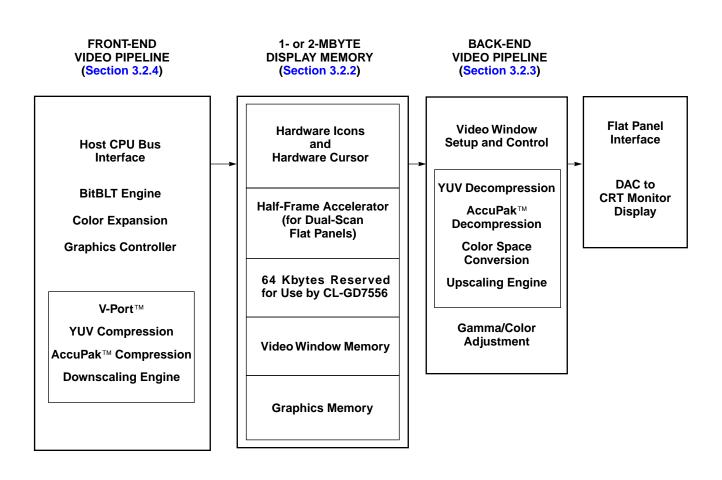

| 3.2        | Enhanced MotionVideo™ Acceleration                                                          | 3-4  |

| 3.2.1      | MVA Feature Set: Overview                                                                   | 3-4  |

| 3.2.2      | MVA™ Feature Set: Display Memory                                                            | 3-6  |

| 3.2.3      | MVA™ Feature Set: Back-End Video Pipeline                                                   | 3-10 |

| 3.2.4      | MVA™ Feature Set: Front-End Video Pipeline                                                  | 3-15 |

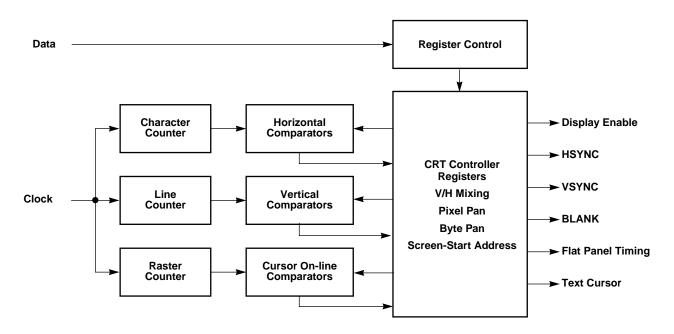

| 3.3        | Functional Blocks                                                                           | 3-32 |

| 3.3.1      | PCI Bus Interface (External/General Register PCI00)                                         | 3-32 |

| 3.3.2      | Host CPU Write Buffer                                                                       | 3-32 |

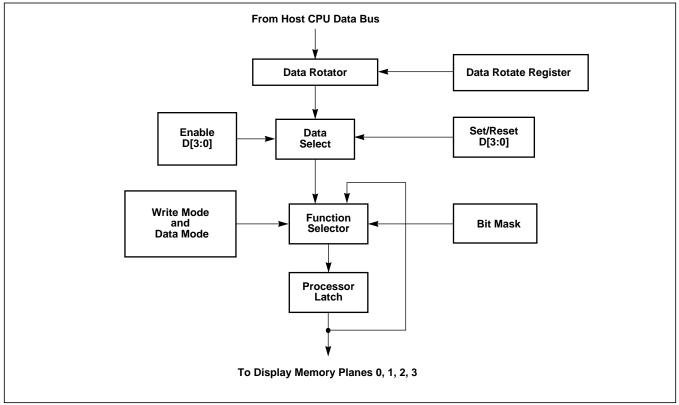

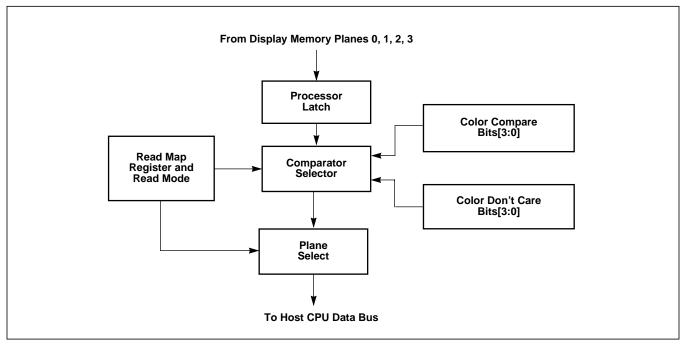

| 3.3.3      | Graphics Controller                                                                         | 3-34 |

| 3.3.4      | Color Expansion (Extension Registers GR10–GR11, GR13, and GR30)                             | 3-36 |

| 3.3.5      | BitBLT Engine (Extension Registers GR20–GR35)                                               | 3-36 |

| 3.3.6      | Memory Arbiter                                                                              | 3-37 |

| 3.3.7      | Memory Sequencer                                                                            |      |

| 3.3.8      | CRT FIFO                                                                                    | 3-38 |

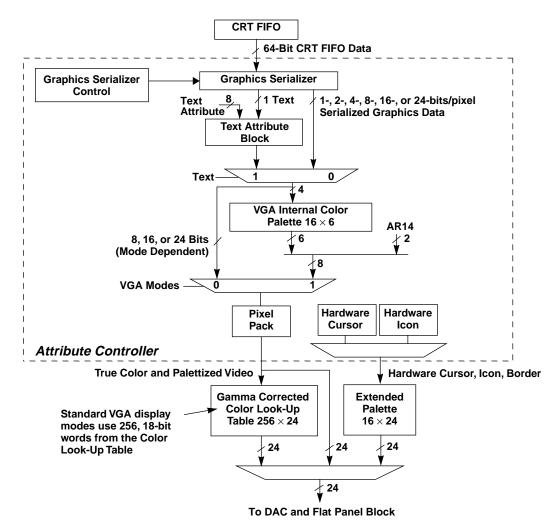

| 3.3.9                                                                                                                                                              | Attribute Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3.10                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.11                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.12                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.13                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.14                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.15                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.16                                                                                                                                                             | , 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                             |

| 3.3.17                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.18                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.19                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.20                                                                                                                                                             | 51 ( 5 ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                             |

| 3.3.21                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.3.22                                                                                                                                                             | 5 5 ( 5 ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |

| 3.3.23                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |

| 3.4                                                                                                                                                                | CL-GD7556 Controller Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                             |

| 3.4.1                                                                                                                                                              | Power Management (Extension Registers CR80 and CR8A–CR8D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |

| 3.4.2                                                                                                                                                              | Surrounding-Graphics Color-Palette Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                             |

| 3.4.3                                                                                                                                                              | Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                             |

| 3.4.4                                                                                                                                                              | Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                             |

| 3.4.5                                                                                                                                                              | Configuration Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                             |

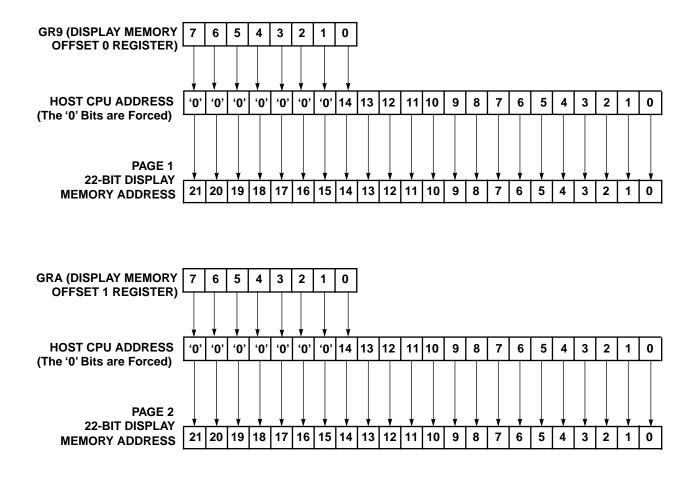

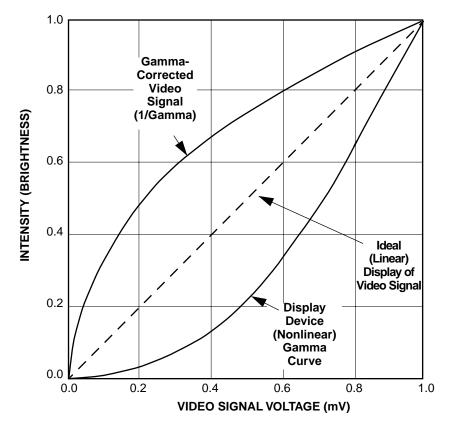

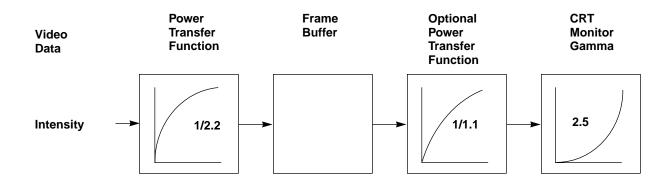

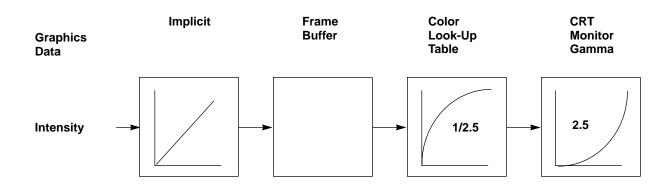

| 3.5                                                                                                                                                                | Software Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |