M 9278788 0000222 6 M

PRELIMINARY

# HCGA CONTROLLER

T-52-33-47

UM487

#### Features

- MGA (Hercules) and CGA compatible

- Built-in 6845 CRTC

- 64K Bytes of video memory

#### **General Description**

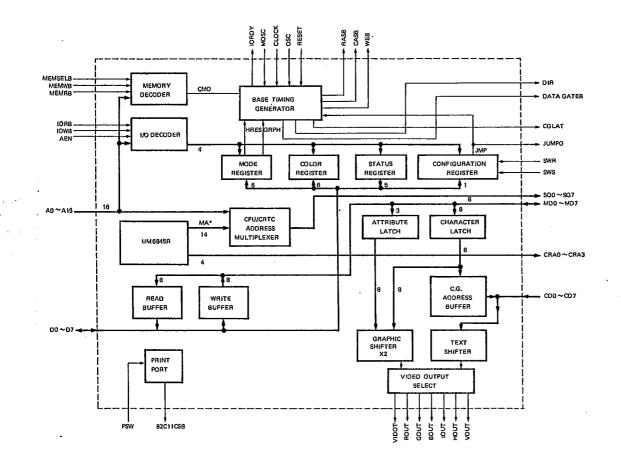

The UM487 single-chip HCGA controller is an advanced product designed to serve as a combination MGA and CGA through the integration of most of the circuits found on MGA and CGA cards. Built with the UMC  $2\mu$ m CMOS process, the UM487 incorporates a built-in 6845 CRTC circuit, Thus, for MGA and CGA functions, only a few

Flicker-Free operation during CPU read/write

- Minimum circuit board space required

- Display mode changeable using hardware or software

- Optional primary printer port

external components are required to complete the circuits. These include: 64K bytes DRAM; 4 TTLs (74LS374, 74LS245 74LS04 and 74LS20); one character generator (UM2310) and a 16.257 MHz crystal. The UM487 comes packaged in a compact, 100-pin plastic flat pack.

. . . . . .

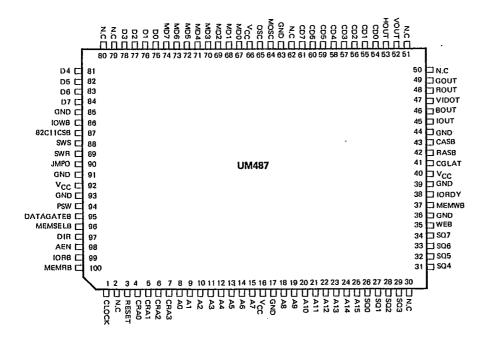

# **Pin Configuration**

D

24E

<u>.</u>....

. مە

umc

.....

UM487

T-52-33-47

# **Block Diagram**

**-** -

📕 9278788 0000224 T 🎟

. .....

,

**UM487**

T-52-33-47

### Absolute Maximum Ratings \*

.

| Operating Temperature                    |  |

|------------------------------------------|--|

| Storage Temperature                      |  |

| All Output Voltages                      |  |

| All Input Voltages                       |  |

| Supply Voltage V <sub>CC</sub> 0V to +7V |  |

| Power Dissipation                        |  |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC** Electrical Characteristics $(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } 70^{\circ}C)$

| Symbol           | Parameter                      | Min, | Typ. | Max. | Unit | Condition                             |

|------------------|--------------------------------|------|------|------|------|---------------------------------------|

| VIH              |                                | 2.0  |      |      | V    |                                       |

| VIL              | Input Voltage                  |      |      | 0.8  | V    |                                       |

| V <sub>OH1</sub> | Output Voltage (for SQ0 ~ SQ7  | 2.4  |      |      | V    | l <sub>OH</sub> = -6.0 mA             |

| V <sub>OL1</sub> | IORDY, RASB, CASB, WEB)        |      |      | 0.4  | V    | l <sub>OL</sub> = +6.0 mA             |

| V <sub>QH2</sub> |                                | 2.4  |      |      | V    | l <sub>OH</sub> = -3.0 mA             |

| VOL2             | Output Voltage (other outputs) |      |      | 0.4  | V    | I <sub>OH</sub> = +3.0 mA             |

| I <sub>IL</sub>  | Input Leakage                  | -10  |      | +10  | μA   | $0 \leqslant V_{in} \leqslant V_{CC}$ |

| lol              | Output Leakage                 | -10  |      | +10  | μA   |                                       |

| I <sub>OP</sub>  | Operating Current              |      |      | +12  | mA   |                                       |

24E D

\*Comments

# Display

-

. جديد ا

¥ z

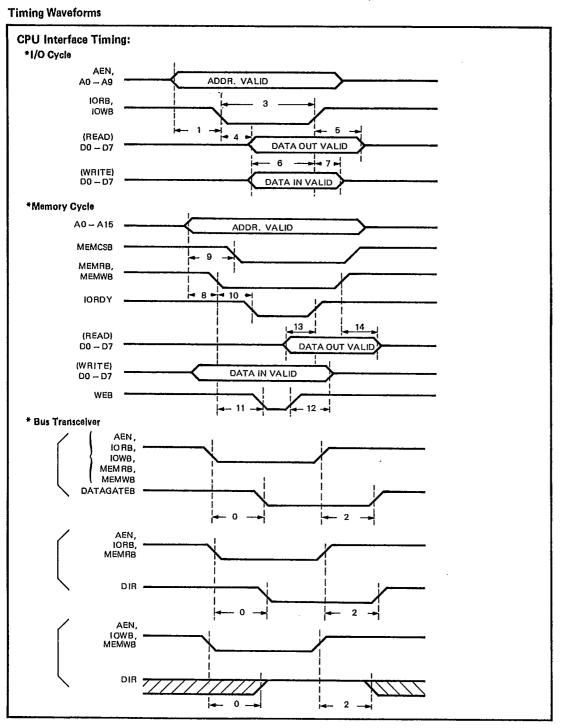

AC Characteristics (CGA MODE BASE CLOCK 14.318 MHz, MGA MODE BASE CLOCK 16.257 MHz) C-1 CPU Interface

| No. | Symbol            | Parameter                                                          | Min. | Тур. | Max. | Unit |

|-----|-------------------|--------------------------------------------------------------------|------|------|------|------|

| 0   | <sup>t</sup> dac  | DIR, DATAGATEB Active to CPU I/O or<br>Memory Read/Write Cycle     |      |      | ·25  | ns   |

| 1   | t <sub>ASI</sub>  | Address Setup Time to IORB, IOWB                                   | - 30 |      |      | ns   |

| 2   | <sup>t</sup> dNC  | DIR, DATAGATEB Non-active to CPU I/O or<br>Memory Read/Write Cycle |      |      | 20   | ns   |

| 3   | t <sub>IPW</sub>  | IORB, IOWB Active Pulse Width                                      | 160  |      |      | ns   |

| 4   | <sup>t</sup> DOIR | Data Output Valid Time to IORB                                     |      |      | 20   | ns   |

| 5   | t <sub>ohir</sub> | Data Output Valid Hold Time to IORB                                | 30   |      |      | ns   |

| 6   | <sup>t</sup> DSIW | Data in Setup Time to IOWB                                         | 30   |      |      | ns   |

| 7   | t <sub>DHIW</sub> | Data in Hold Time to IOWB                                          | 10   |      |      | ns   |

| 8   | t <sub>ASM</sub>  | Address Setup Time to MEMRB, MEMWB                                 | 0    |      |      | ns   |

| 9   | <sup>t</sup> AMD  | Addr. Valid to MEMCSB Active Delay                                 |      |      | 15   | ns   |

| 10  | t <sub>MID</sub>  | MEMRB, MEMWB Active to IORDY Low Delay                             |      |      | 30   | ns   |

| 11  | <sup>t</sup> MWED | MEMWB Active to WEB Active Delay 10                                |      |      | 2240 | ns   |

| 12  |                   | Memory Write Data Hold Time to WEB                                 | 10   |      |      | ns   |

**.**....

**1** 9278788 0000225 1 **1**

,

T-52-33-47

UM487

.

.

# C-1 CPU Interface (Continued)

| No, | Symbol            | Parameter                             |    | Тур. | Max. | Unit |

|-----|-------------------|---------------------------------------|----|------|------|------|

| 13  | t <sub>DORD</sub> | MEMRB Data Output Valid to IORDY      | 20 | 30   |      | ns   |

| 14  | <sup>t</sup> DOMR | MEMRB Data Output Valid Hold to MEMRB | 20 |      |      | ns   |

24E D

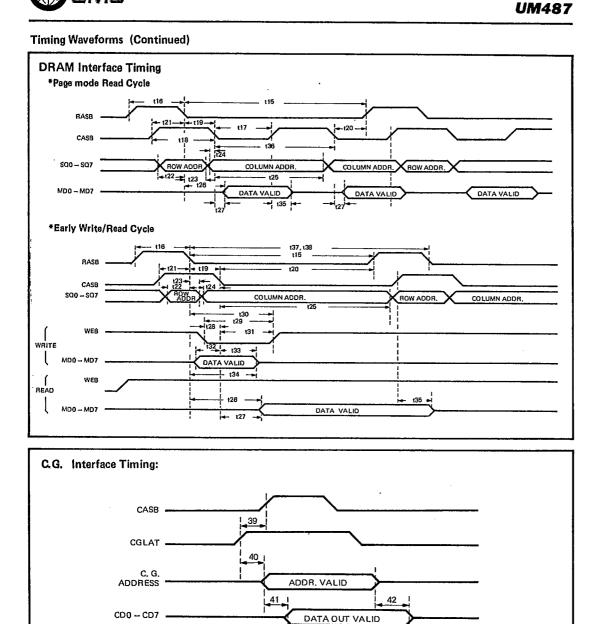

# C-2 DRAM Interface

| No. | Symbol            | Parameter                        | Min. | Тур. | Max. | Unit |

|-----|-------------------|----------------------------------|------|------|------|------|

| 15  | t <sub>RL</sub>   | RASB Low Time                    |      | 150  |      | ns   |

| 16  | t <sub>RH</sub>   | RASB High Time                   |      | 90   |      | ns   |

| 17  | <sup>t</sup> CL   | CASB Low Time                    |      | 90   |      | ns   |

| 18  | <sup>t</sup> сн   | CASB High Time                   |      | 60   |      | ns   |

| 19  | <sup>t</sup> ricl | RASB to CASB                     |      | 60   |      | ns   |

| 20  | <sup>t</sup> CLRH | CASBto RASB                      |      | 60   |      | ns   |

| 21  | <sup>t</sup> chrl | CASB _ to RASB                   |      | 60   |      | ns   |

| 22  | t <sub>RSU</sub>  | Row Address Setup Time to RASB   | 0    |      |      | ns   |

| 23  | t <sub>RHL</sub>  | Row Address Hold Time to RASB    | 20   |      |      | ns   |

| 24  | tcsu              | Column Addr. Setup Time to CASB  | 0    |      |      | ns   |

| 25  | <sup>t</sup> снь  | Column Addr. Hold Time to CASB   | 25   |      |      | ns   |

| 26  | <sup>t</sup> ACR  |                                  |      |      | 150  | ns   |

| 27  | t <sub>ACC</sub>  |                                  |      |      | 90   | ns   |

| 28  | twcl.             | WEB Active before CASB           |      | 40   |      | ns   |

| 29  | <sup>t</sup> wpw  | WEB Active Pulse Width           |      | 90   |      | ns   |

| 30  | t <sub>RLW</sub>  | RASB to WEB Active Hold          |      | 150  |      | ns   |

| 31  | <sup>t</sup> CAW  | CASB to WEB Active Hold          |      | 60   | 1    | ns   |

| 32  | twosc             | Write Data Setup Time to CASB    | 0    |      |      | ns   |

| 33  | <sup>t</sup> wdhc | Write Data Hold Time to CASB     | 45   |      |      | ns   |

| 34  | twohr             | Write Data Hold Time to RASB     | 110  |      |      | ns   |

| 35  | t <sub>DODC</sub> | Data Output Disable Time to CASB | 0    |      |      | ns   |

| 36  | t <sub>PCYC</sub> | Page Mode Read Cycle Time        | 150  |      |      | ns   |

### C-3 C. G. Interface

į

| No, | Symbol            | Parameter                          | Min. | Тур. | Max. | Unit |

|-----|-------------------|------------------------------------|------|------|------|------|

| 39  | t <sub>CGCH</sub> | CGLAT to CASB                      | 5    |      | 10   | ns   |

| 40  | tCGAD             | CGLAT to C. G. Address Valid Delay |      |      | 10   | ns   |

| 41  | tACC              | C. G. Access Time                  |      |      | 250  | ns   |

| 42  | t <sub>DOHA</sub> | Data Output Hold Time from Addr.   | 0    |      |      | ns   |

**.** .

• ....

🔳 E 2520000 887875P

T-52-33-47

UM487

#

,

24E D

Display

-

3--7

**\_** -

9278788 0000227 5

,

# Т-52-33-47

24E D

**.** . .

.....

T-52-33-47

UM487

,

# Pin Description

| Pin No.            | Symbol                 | 1/0 | Description                                                            |

|--------------------|------------------------|-----|------------------------------------------------------------------------|

| 1                  | CLOCK                  | 1   | CPU clock generates built-in 6845 enable signal                        |

| 3                  | RESET                  | 1   | Chip reset signal, active high                                         |

| 4~7                | CRA0~CRA3              | 0   | Internal 6845 scan line counter, CRA0 is LSB                           |

| 8 ~ 15<br>18~25    | A0 ~ A7<br>A8 ~ A15    | 1   | CPU address bits 0~15, A0 is LSB<br>A15 is MSB                         |

| 26 ~ 29<br>31 ~ 34 | SQ0 ~ SQ3<br>SQ4 ~ SQ7 | 0   | Video memory (DRAM) address, SQ0 is LSB                                |

| 35                 | WEB                    | 0   | Active low, video memory write strobe signal                           |

| 37                 | MEMWB                  | 1   | Active low, CPU memory write signal                                    |

| 38                 | IORDY                  | 0   | Active high, informs CPU cycle is completed                            |

| 41                 | CGLAT                  | 0   | Code data latch to C, G. during CGLAT rising edge                      |

| 42                 | RASB                   | 0   | Video memory row address strobe signal                                 |

| 43                 | CASB                   | 0   | Video memory column address strobe signal                              |

| 45                 | IOUT                   | 0   | Intensity signal output to RGB monitor                                 |

| 46                 | BOUT                   | 0   | Blue signal output to RGB monitor                                      |

| 47                 | VIDOT                  | 0   | Video dot stream output to monitor                                     |

| 48                 | ROUT                   | 0   | Red signal output to RBG monitor                                       |

| 49                 | GOUT                   | 0   | Green signal output to RBG monitor                                     |

| 52                 | VOUT                   | 0   | Vertical synchronous output to monitor                                 |

| 53                 | ноит                   | 0   | Horizontal synchronous output to monitor                               |

| 54 ~ 61            | CD0 ~ CD7              |     | Character Generator (C. G.) data bus, CD0 is first pixel               |

| 64                 | MOSC                   |     | MGA mode base clock input (16.257 MHz crystal)                         |

| 65                 | OSC                    | 1   | CGA mode base clock input (14.318 MHz crystal)                         |

| 67~74              | MD0 ~ MD7              | 1/0 | Video memory data bus, MD0 is LSB                                      |

| 75 ~ 78<br>81 ~ 84 | D0 ~ D3<br>D4 ~ D7     | 1/0 | Data bus, D0 is LSB                                                    |

| 86                 | IOWB                   | 1   | Active low, CPU I/O write signal                                       |

| 87                 | 82C11CSB               | 0   | Active low, printer controller UM82C11 chip select                     |

| 88                 | SWS                    | 1   | Active high, to select CGA mode                                        |

| 89                 | SWR                    | 1   | Active high, to select MGA mode                                        |

| 90                 | JMPO                   | 0   | Select CGA/MGA C. G. character font, '0' for MGA                       |

| 94                 | PSW                    | 1   | Enables primary printer port while PSW is connected to UM82C11 CSB pin |

| 95                 | DATAGATÉB              | 0   | Active low, enables external data transceiver 74LS245                  |

24E D

3–9

\_\_ ~

1

UM487

-----

Т-52-33-47

ł

# Pin Description (Continued)

| Pin No,                            | Symbol          | 1/0 | Description                                                                                                                                                     |

|------------------------------------|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 96                                 | MEMSELB         | 1   | Active low to select video memory while CPU pins A19 $\sim$ A16 are equal to '1011'                                                                             |

| 97                                 | DIR             | 0   | Controls external bus transceiver 74LS245 direction<br>'0': from UM487 to CPU during IORB or MEMRB active<br>'1': from CPU to UM487 during IOWB or MEMWB active |

| 98                                 | AEN             | 1   | Active low to enable I/O address                                                                                                                                |

| 99                                 | IORB            | 1   | Active low, CPU I/O read signal                                                                                                                                 |

| 100                                | MEMRB           | 1   | Active low, CPU memory read signal                                                                                                                              |

| 2,30,50<br>51,62,<br>79,80         | N. C.           | *   | No connection                                                                                                                                                   |

| 17, 36, 85<br>39, 44, 93<br>63, 91 | GND             | I   | Ground                                                                                                                                                          |

| 16, 40<br>66, 92                   | V <sub>cc</sub> | 1   | +5V power supply                                                                                                                                                |

24E D

\* For proper operation, these pins should not be connected.

# **Register Description**

# A. Register:

.

| I/O A | ddress d |            |                                       |                                       |

|-------|----------|------------|---------------------------------------|---------------------------------------|

| MGA   | CGA      | Read/Write | Function                              | Note                                  |

| 3B4   | 3D4      | W          | 6845 index register                   | refer to                              |

| 3B5   | 3D5      | ₽/W        | 6845 data register                    | UM6845R                               |

| 388   | 3D8      | W          | Mode control register                 |                                       |

|       | 3Ď9      | W          | Color select register                 | · · · · · · · · · · · · · · · · · · · |

| 3BA   | 3DA      | R          | Status register                       |                                       |

| 388   | 3DB      | w          | Light pen reset register              |                                       |

| 389   | 3DC      | w          | Light pen set register                | · · · · · · · · · · · · · · · · · · · |

| 31    | BF       | w          | Configuration register                |                                       |

| 31    | вС       | R/W        | Primary printer data register         |                                       |

| 31    | BD       | R          | Primary printer status register       | refer to                              |

| ЗВЕ   |          | R/W        | Primary printer control word register | UM82C11                               |

'---' means not used

- - -

T-52-33-47

UM487

.

-

100 A.V.A.

# A-1 Status Register (3?A)

| Bit | Logic | MGA (3BA)                   | CGA (3DA)              |

|-----|-------|-----------------------------|------------------------|

| 0   | 0     | Non-horizontal sync. period | Display active period  |

|     | 1     | Horizontal sync. period     | Non-display period     |

| 1   | 0     | Light pen reset             | Light pen reset        |

|     | 1     | Light pen sat               | Light pen set          |

| 2   | 0     | Light pen switch off        | Light pen switch off   |

|     | 1     | Light pen switch on         | Light pen switch on    |

| 3   | 0     | Video dot off               | Non-vert. sync. period |

|     | 1     | Video dot on                | Vertical sync. period  |

| 7   | 0     | Vertical sync. period       |                        |

|     | 1     | Non-vertical sync. period   |                        |

24E D

Bits 4, 5 and 6 not used

### A-2 Mode Controller Register (3?8)

| Bit | Logic | MGA (3B8)                          | CGA (3D8)           |

|-----|-------|------------------------------------|---------------------|

| 0   | 0     |                                    | 40*25 Text          |

|     | 1     |                                    | 80*25 Text          |

| 1   | 0     | Text                               | Text                |

|     | 1     | Graphic (while $3BF$ bit $0 = 1$ ) | Graphic             |

| 2   | 0     |                                    | Color mode          |

|     | 1     |                                    | Black/white         |

| 3   | 0     | Disable video                      | Disable video       |

|     | 1     | Enable video                       | · Enable video      |

| 4   | 0     |                                    | 320*200 Graphic     |

|     | 1     |                                    | 640*200 Graphic     |

| б   | 0     | Disable blink                      | Disable blink       |

|     | 1     | Enable blink                       | Enable blink        |

| 6   | 0     | Disable change mode                | Disable change mode |

|     | 1     | Enable change mode                 | Enable change mode  |

| 7   | 0     | Page O                             |                     |

|     | 1     | Page 1 (while 3BF bit 1 = 1)       |                     |

-

-----

,

# **UM487**

T-52-33-47

#### A-3 Color Select Register (3D9 CGA Only)

A-5 Internal Registers of 6845 (Refer to UM6845R/RA/RB Data Sheet)

| Bit | Function                                                                                                                                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | In 40*25 text, select blue of border color<br>In 320*200 graphic, select blue of back-<br>ground color<br>In 640*200 graphic, select blue of foreground<br>color              |

| 1   | In 40*25 text, select green of border color<br>In 320*200 graphic, select green of back-<br>ground color<br>In 640*200 graphic, select green of fore-<br>ground color         |

| 2   | In 40*25 text, select red of border color<br>In 320*200 graphic, select red of background<br>color<br>In 640*200 graphic, select red of foreground<br>color                   |

| 3   | In 40*25 text, select intensity of border color<br>In 320*200 graphic, select intensity of<br>background color<br>In 640*200 graphic, select intensity of<br>foreground color |

| 4   | Text mode background color or<br>Graphic mode foreground color                                                                                                                |

| 5   | Select foreground color pair (only 320*200<br>graphic)                                                                                                                        |

| Register<br>No. | Function                     | Unit  | Read/<br>Write |

|-----------------|------------------------------|-------|----------------|

| RO              | Horizontal total             | Char. | w              |

| R1              | Horizontal display           | Char, | w              |

| R2              | Horizontal sync.<br>position | Char. | w              |

| R3              | Sync. pulse width            | Char, | w              |

| R4              | Vertical total               | Row   | w              |

| R5              | Vertical total<br>adjust     | Line  | w              |

| R6              | Vertical display             | Row   | w              |

| R7              | Vertical sync.<br>position   | Row   | w              |

| R8              | Non-interlace mode           |       | w              |

| R9              | Max. scan line               | Line  | w              |

| R10             | Cursor start                 | Line  | w              |

| R11             | Cursor end                   | Line  | w              |

| R12             | Start address (H)            |       | w              |

| R13             | Start address (L)            |       | w              |

| R14             | Cursor address (H)           |       | R/W            |

| R15             | Cursor address (L)           |       | R/W            |

| R16             | Light pen address (H)        |       | R              |

| R17             | Light pen address (L)        |       | R              |

Bits 6, 7 not used

# A-4 Configuration Register (3BF)

| Bit | Logic  | Function                                                                     |

|-----|--------|------------------------------------------------------------------------------|

| 0   | 0<br>1 | Disable MGA graphic<br>Enable MGA graphic                                    |

| • 1 | 0<br>1 | Disable MGA page 1<br>Enable MGA page 1                                      |

| 6   | 0<br>1 | Select MGA mode (while 3D8 bit6 = 1)<br>Select CGA mode (while 3B8 bit6 = 1) |

Other bit not used

. . .

# MC

,

#### **Functional Description**

#### **B-1 By HARDWARE**

The MGA mode is selected when SW1 pin 2 is connected to pin 3, otherwise CGA mode is active if SW1 pin 2 is connected to pin 1. ••

24E D

#### **B-2 By SOFTWARE**

The software changes display mode only if SW3 pin 2 is connected to pin 3 and 378 bit 6 is equal to high, (where ? is D or B)

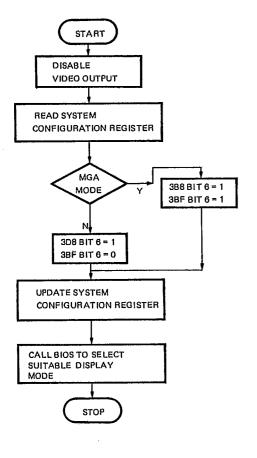

### **Program Flowchart:**

| B-3 Pro | gram Listing | I              | . <b>.</b> .                              |

|---------|--------------|----------------|-------------------------------------------|

| NCOMN   | PROC         | NEAR           | · ·                                       |

|         | ASSUME       | CS: CODE, C    | DS: DATA, SS: STACK                       |

|         | PUSH         | DS             |                                           |

|         | MOV          | AX,0           |                                           |

|         | PUSH         | AX             |                                           |

|         | PUSH         | CS             |                                           |

|         | POP          | DS             |                                           |

|         | MOV          | AL, 20H        |                                           |

|         | MOV          | CX,07D0H       |                                           |

|         | MOV          | вн, о          |                                           |

|         | MOV          | BL,07          |                                           |

|         | MOV          | AH, 09         | ; clear video memory                      |

|         | INT          | 10H            |                                           |

|         | MOV          | AH, OFH        | ; read video state                        |

|         | INT .        | 10H            | • • • • • • • • • • • • • • • • • • • •   |

|         | CMP          | AL, 07         | ; MGA mode?                               |

|         | JZ           | MMM            |                                           |

|         | JMP          | CCC            |                                           |

| MMM:    | MOV          | AL,40H         | ; MGA mode                                |

|         | MOV          | DX, 388H       | ; enable change mode                      |

| •       | OUT          | DX, AL         |                                           |

|         | MOV          | DX, 3BFH       |                                           |

|         | OUT          | DX, AL         | ; change to CGA mode                      |

|         | MOV          | AX, 0          |                                           |

|         | MOV          | DS, AX         |                                           |

|         | MOV          | AL, (410]      | ; read BIOS configura-                    |

|         |              |                | tion register                             |

|         | AND          | AL, CFH        | ; isolate bits 4, 5                       |

|         | OR           | AL, 20H        | ; update BIOS con-                        |

|         |              |                | figuration register                       |

|         | MOV          | [410], AL      | ; to CGA mode                             |

|         | MOV          | AH, 0          | ; select CGA                              |

|         | .MOV         | AL, 3          |                                           |

|         | INT          | 10H            |                                           |

|         | JMP          | END            |                                           |

| CCC:    | MOV          | AL,40H         | ; CGA mode                                |

|         | MOV          | DX, 3D8H       |                                           |

|         | OUT          | DX, AL         | ; enable change mode                      |

|         | MOV          | AL,0           |                                           |

|         | MOV          | DX, 3BFH       | ; change to MGA mode .                    |

|         | OUT          | DX, AL         |                                           |

|         | MOV          | AX,0           |                                           |

|         | MOV          | DX, AX         |                                           |

|         |              | AL, [410]      |                                           |

|         |              |                | t undata BIOS and                         |

|         | OR           | AL, 30H        | ; update BIOS con-<br>figuration register |

|         | MOV          | [410], AL      | ; to MGA mode                             |

|         | MOV          | AH, 0          | ; select MGA                              |

|         | MOV          | АП, О<br>АЦ, 7 |                                           |

|         | INT          | 10H            |                                           |

| END:    | RET          | 1011           |                                           |

| NCOMN   |              |                |                                           |

| 1,001   |              |                |                                           |

9278788 0000232 9 🛲

T-52-33-47

UM487

••

1.1

---

9278788 0000233 0 📰

,

T-52-33-47

· · · · ·

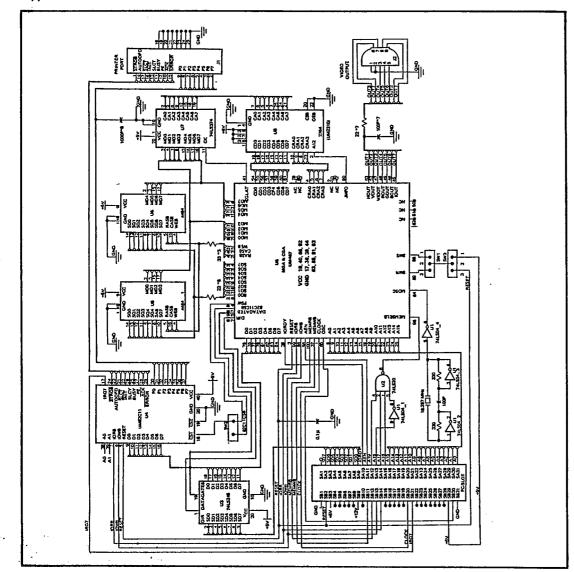

**Application Circuits**

24E D

The 74LS04 is used for crystal circuit 1.

2. The 74LS20 decodes CPU A19 ~ A16 to generate MEMCSB while MGA or CGA video memory is selected

3-14

The 74LS245 is data transceiver between CPU and UM487 З.

4. The 74LS374 latches code data to C. G. during text mode

- SW1 3 2 1 : MGA mode 5.

- SW1 3 2 1 : CGA mode

- 6. SW2 is connected while primary printer port is selected

SW3 3 2 1 : Enable change mode by software SW3 3 2 1 : Enable change mode by software 7.

📰 9278788 0000234 2 🎫

T-52-33-47

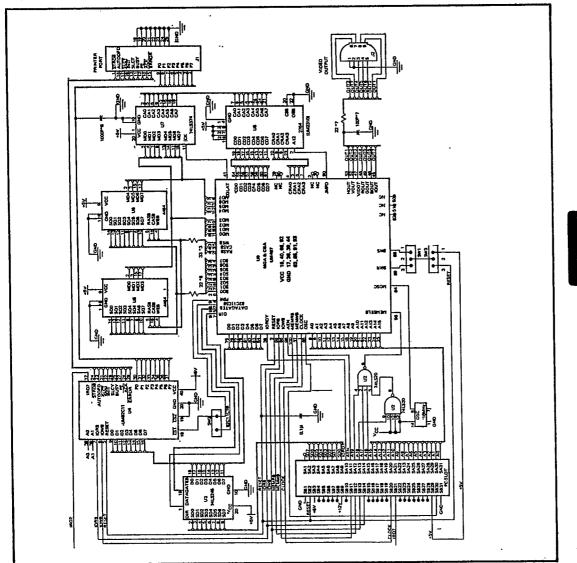

# Application Circuits

24E D

1. 16 MHz osc for MGA mode

2. The 74LS20 decodes CPU A19 ~ A16 to generate MEMCSB while MGA or CGA video memory is selected

3. The 74LS245 is data transceiver between CPU and UM487

4. The 74LS374 latches code data to C. G. during text mode

5. SW1 321: MGA mode

SW1 321: CGA mode

- 6. SW2 is connected while primary printer port is selected

- 7. SW3 321: Enable change mode by software

SW3 321: Disable change mode by software

3—15

-----

24E D 🖬 9278788 0000235 4 📰

T-52-33-47

Ordering Information

| Part No. | Package     |

|----------|-------------|

| UM487F   | 100 Pin QFP |

.

UM487

3–16

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.