# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 3D GRAPHICS ACCELERATOR **POWER VR™** µPD62011

The  $\mu$ PD62011 is a 3D graphics accelerator LSI designed for personal computers of the PowerVR 3D graphics processor family.

The  $\mu$ PD62011 realizes high performance system by adding functions such as bi-linear texture and 66-MHz PCI bus support to the  $\mu$ PD62010 and incorporating a circuit that supports geometry operations performed in the CPU.

#### **FEATURES**

- Pin-compatible/software-compatible with the  $\mu$ PD62010

- Interface conforming with PCI bus 2.1 (supports 66 MHz)

- On-chip hidden surface removal (Z buffer unnecessary, per pixel, 32-bit depth precision)

- · Automatic shadow generation by hardware

- Per-pixel fogging

- 66-MHz operation

- · On-chip geometry processing support circuit

- · Texture mapping

- · Perspective correct texture mapping

- MIP mapping

- · Bi-linear texture

- 16-/8- bit texture

- Translucent texture

- Texture memory: 1 to 4 Mbytes

- Shading

- · Smooth shading

- · Flat shading/Highlighting

- Output Image

- RGB/BGR 565 Packed, RGB/BGR 555 Packed

- RGB/BGR 888 Packed/Unpacked

- · Little/Big endian pixel format

- Maximum 1024 × 1024 resolution

- Supported API

- Dedicated API (PowerSGL<sup>TM</sup>)

- Microsoft's Direct3D™

#### **ARCHITECTURE**

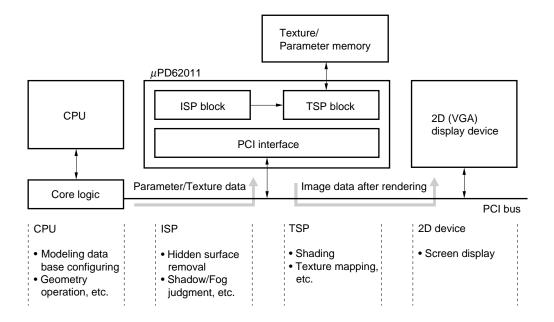

The PowerVR system is a 3D graphics technology featuring an original architecture in order to resolve the intrinsic cost/performance problem of conventional 3D graphics systems. The most typical functions, hidden surface removal and plane modeling, are described below.

#### 1. Hidden Surface Removal

Conventional 3D graphics systems employ the Z-buffer that compares the z value (depth) of each polygon-configuring pixel when performing hidden surface removal (removing data invisible from the viewpoint). The memory requirement for 32-bit depth at  $640 \times 480$  pixels is 1.2 Mbytes, which greatly affects the cost of the system. Moreover, because memory access must be executed the same number of times as the number of polygons that include the pixel for which hidden surface removal is to be performed, the system performance is affected by the memory band width (data transfer performance).

In the PowerVR architecture, the display is divided into  $32 \times 32$  pixels or  $64 \times 64$  pixels segments called tiles and hidden surface removal is performed within the device. Accordingly, since no Z-buffer is necessary and the data written into the frame buffer is only the forefront visible pixel data, high performance 3D systems not limited by the memory system can be realized.

#### 2. Plane Modeling

In addition to the conventional polygon modeling method (configuring with triangles and squares), PowerVR employs the method of modeling with an infinite plane (defining an area enclosed by planes as an object). The data (x, y, z) of each vertex of the polyhedron that configures the object is required in the polygon modeling method. On the other hand, in plane modeling, data is defined using only a normal vector and a point on a plane, which considerably reduces the amount of data. This data reduction directly contributes to reducing the processing time. Additionally, a unique function that performs real-time and automatic shadow generation for effective 3D rendition by using plane modeling is realized.

# OUTLINE OF $\mu$ PD62011 FUNCTIONS

The  $\mu$ PD62011 extends the functions of the  $\mu$ PD62010 and improves 3D graphics rendering, while realizing high performance.

# 1. Bi-linear Texture Mapping

The  $\mu$ PD62010 employs the MIP mapping function for precise texture mapping. MIP mapping is a precise texture mapping method (2-point texture) in which the texture to be mapped is prepared in advance, and then data is sampled from a large and small texture sheets corresponding to the object.

The  $\mu$ PD62011 enhances the function of the  $\mu$ PD62010 and supports bi-linear texture mapping. In data sampling in the core of MIP mapping, mapping is performed by interpolating two points from each texture (4-point texture).

#### 2. 66-MHz PCI Bus Interface

In the PowerVR system, the parameters/data for 3D image processing are captured via the PCI bus, and the generated 3D images are transferred to the 2D system via the PCI bus. The  $\mu$ PD62011 provides an interface compatible with the 66-MHz spec of PCI bus, which enables high-speed parameter transfer/image data transfer.

# 3. Floating Point Format Conversion Circuit

In the PowerVR system, parameters A and B of the plane equation Ax + By + C are processed in the 20-bit floating point format, and parameter C is processed in the 20-bit fixed point format.

In the  $\mu$ PD62010, conversion from the IEEE floating point format to the above data format is performed by software. On the other hand, the  $\mu$ PD62011, which incorporates a format conversion circuit, enables loading of parameter data in the IEEE floating point format which enables high-speed processing by reducing the software load.

#### 4. On-chip Pointer Register

When loading the parameters or object data in the main memory, the  $\mu$ PD62010 references the pointer table configured in memory but the  $\mu$ PD62011 accesses data directly because it has a pointer register. Moreover, successive data loading is enabled by the pointer chain function.

# 5. Output Image Mask Function

Since the PowerVR architecture adopts 3D screen processing in tile units, when adding 3D objects on a 2D background, the background color of tiles must be made transparent. The  $\mu$ PD62010 does this by software, while, the  $\mu$ PD62011 does this by masking the output image in pixel units.

# 6. Edge Sharing

When processing a polygon mesh structure, the amount of data processing is reduced greatly by sharing the data regarding the boundary edges of neighboring polygons.

#### 7. Software-Compatible with $\mu$ PD62010

The  $\mu$ PD62011 is compatible with the  $\mu$ PD62010 in the initial state immediately after reset. This function is enabled by register setting.

The main function of the ISP block is performing hidden surface removal for an object list in a 3D space. The output of the ISP block is the ID of the visible surface corresponding to each pixel. Hidden surface removal carried in the ISP block has a precision equivalent to that of conventional Z buffering. As a result, when processing with a precision identical that of a 32-bit Z buffer is performed, the  $\mu$ PD62011 does not require a Z buffer memory. Moreover, the ISP block supports the shadow casting function indicating whether a shadow is generated in the visible surface.

The TSP block mainly performs precise texture mapping and shading for the ID of the visible surface supplied by the ISP. The TSP also enables perspective correct texture mapping, smooth shading, transparent face overlaying, and fogging. Besides, the TSP block provides a method for processing visible surface with a minimum number of accesses to texture data stored in an external SDRAM. Both the ISP and TSP blocks have internal caches enabling an efficient local access for rendering parameters stored in these caches.

The PCI bus interface is provided with both master and slave functions for efficient operation. When the  $\mu$ PD62011 reads the parameters related to the ISP block from the system memory, the PCI bus interface functions as PCI master and when it receives the parameters related to the TSP block, it functions as a PCI slave. The PCI bus interface performs optimum buffering for transferring data securely at high speed. The SDRAM/SGRAM controller is designed to allow the blocks in the  $\mu$ PD62011 to share external SDRAM/SGRAM.

The  $\mu$ PD62011 receives the parameters required for rendering via PCI bus and transfers 3D images with texture mapping or shading to the PCI address space. The 3D images data from the  $\mu$ PD62011 is transferred to the 2D graphics (VGA<sup>TM</sup> controller) frame buffer allocated in the PCI address space.

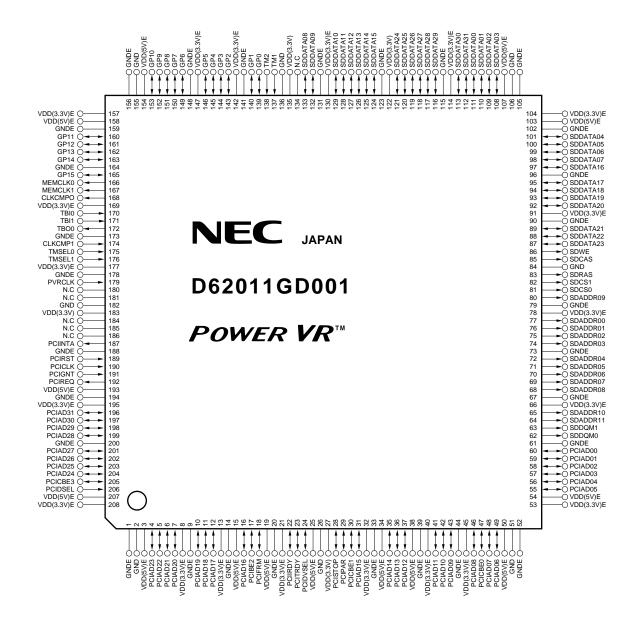

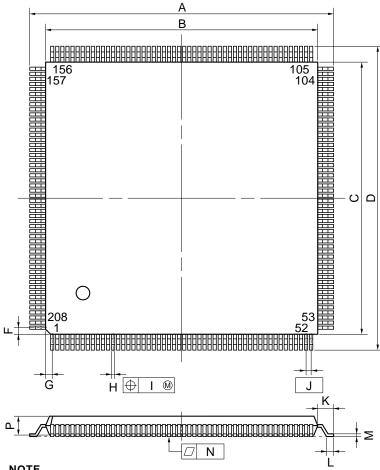

# PIN CONFIGURATION (Top View)

#### 208-PIN PLASTIC QFP (28 $\times$ 28 mm)

# **PIN FUNCTION LIST**

| Pin Name       | Function                                         |  |

|----------------|--------------------------------------------------|--|

| PCIFRM         | PCI Cycle Frame                                  |  |

| PCIIRDY        | PCI Initiator Ready                              |  |

| PCITRDY        | PCI Target Ready                                 |  |

| PCIDVSEL       | PCI Device Select                                |  |

| PCISTOP        | PCI Stop/Disconnect                              |  |

| PCIPAR         | PCI Parity                                       |  |

| PCIINTA        | PCI Interrupt A                                  |  |

| PCIRST         | PCI Reset, used as master reset for the μPD62011 |  |

| PCICLK         | Clock for PCI Interface                          |  |

| PCIGNT         | PCI Master Grant                                 |  |

| PCIREQ         | PCI Master Request                               |  |

| PCICBE0 to 3   | PCI Bus Command and Byte Enables                 |  |

| PCIIDSEL       | PCI Initialization Device Select                 |  |

| PCIAD00 to 31  | PCI Address Data Bus                             |  |

| SDDQM0 to 1    | Memory Request                                   |  |

| SDADR00 to 11  | Memory Address Bus                               |  |

| SDCS0 to 1     | Memory Chip Select                               |  |

| SDRAS          | Memory Row Address Strobe                        |  |

| SDCAS          | Memory Column Address Strobe                     |  |

| SDWE           | Memory Write Enable                              |  |

| SDDATA00 to 31 | Memory Data Bus                                  |  |

| GP0 to 15      | General Purpose I/O Port                         |  |

| MEMCLK0 to 1   | Memory Clock                                     |  |

| CLKCMPO        | Clock Adjusting Port (Output)                    |  |

| CLKCMPI        | Clock Adjusting Port (Input)                     |  |

| PVRCLK         | Internal Clock                                   |  |

| TM1 to 2       | Test Input                                       |  |

| TBI0 to 1      | Test Input                                       |  |

| TBO0           | Test Output                                      |  |

| TMSEL0 to 1    | Test Input                                       |  |

| VDD (3.3 V)    | Internal Digital VDD (3.3 V)                     |  |

| GND            | Internal Digital GND                             |  |

| VDD (5 V) E    | External Digital VDD (5 V)                       |  |

| VDD (3.3 V) E  | External Digital VDD (3.3 V)                     |  |

| GNDE           | External Digital GND                             |  |

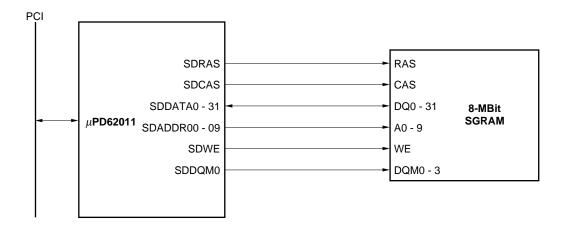

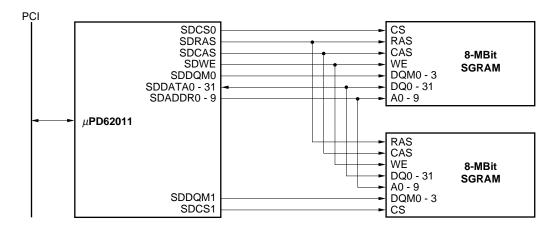

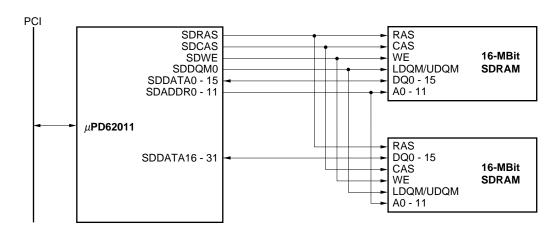

# INTERFACE BETWEEN $\mu$ PD62011 AND MEMORY

# (1) 1 Mbyte

#### (2) 2 Mbytes

# (3) 4 Mbytes

Recommended Devices 8-Mbit SGRAM :  $\mu$ PD481850GF-A12

16-Mbit SDRAM:  $\mu$ PD4516161G5-A10,  $\mu$ PD4516161G5-A12

# **PACKAGE DRAWING**

# 208-PIN PLASTIC QFP (FINE PITCH) (28 $\times$ 28 mm)

#### detail of lead end

# NOTE

Each lead centerline is located within 0.10 mm (0.004 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                            |

|------|------------------------|-----------------------------------|

| Α    | 30.6±0.2               | 1.205±0.008                       |

| В    | 28.0±0.2               | 1.102+0.009                       |

| С    | 28.0±0.2               | 1.102 <sup>+0.009</sup><br>-0.008 |

| D    | 30.6±0.2               | 1.205±0.008                       |

| F    | 1.25                   | 0.049                             |

| G    | 1.25                   | 0.049                             |

| Н    | $0.22^{+0.05}_{-0.04}$ | 0.009±0.002                       |

| ı    | 0.10                   | 0.004                             |

| J    | 0.5 (T.P.)             | 0.020 (T.P.)                      |

| K    | 1.3±0.2                | 0.051±0.008                       |

| L    | 0.5±0.2                | $0.020^{+0.008}_{-0.009}$         |

| М    | $0.17^{+0.03}_{-0.07}$ | 0.007+0.001                       |

| N    | 0.10                   | 0.004                             |

| Р    | 3.2                    | 0.126                             |

| Q    | 0.4±0.1                | 0.016 <sup>+0.004</sup><br>-0.005 |

| R    | 5°±5°                  | 5°±5°                             |

| S    | 3.8 MAX.               | 0.150 MAX.                        |

P208GD-50-LML, MML-2

[MEMO]

# Phase-out/Discontinued

[MEMO]

# Phase-out/Discontinued

PowerVR and PowerSGL are trademarks of VideoLogic Limited.

Direct3D is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

VGA is a trademark of International Business Machines Corporation.

# The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or of others.

M7A 96.10

# For further information, please contact:

#### **NEC Corporation**

NEC Building 7-1, Shiba 5-chome, Minato-ku Tokyo 108-01, Japan Tel: 03-3454-1111

Tel: 03-3454-1111 Fax: 03-3798-6059

#### [North & South America]

#### **NEC Electronics Inc.**

2880 Scott Blvd. Santa Clara, CA 95050-2554 Tel: 408-588-6000 800-366-9782

Fax: 408-588-6130 800-729-5288

#### [Regional Sales Offices]

#### **Central Region**

Greenpoint Tower 2800 West Higgins Road Suite 765 Hoffman Estates, IL 60195

Tel: 847-519-3930 Fax: 847-519-9329

#### **Norcal Region**

3033 Scott Blvd. Santa Clara, CA 95054 Tel: 408-588-5100 Fax: 408-588-5134

#### **Eastern Region**

901 Lake Destiny Drive Suite 320 Maitland, FL 32751, U.S.A. Tel: 407-875-1145 Fax: 407-875-0962

#### Western Region

One Embassy Centre 9020 S.W. Washington Square Road Suite 400 Tigard, OR 97223, U.S.A. Tel: 503-671-0177 Fax: 503-643-5911

#### NEC do Brasil S.A.

Div. Componentes Eletronicos Rodovia Presidente Dutra, KM 218 CEP 07210-902-Jd. Cumbica-Guarulhos-SP, Brasil Tel: 011-6465-6810

Fax: 011-6465-6829

# [Europe]

# **NEC Electronics (Germany) GmbH**

Kanzlerstr. 2, 40472 Düsseldorf Germany Tel: 0211-650302

Fax: 0211-6503490

# Munich Office

Arabellastr. 17 81925 München, Germany Tel: 089-921003-0 Fax: 089-92100315

#### **Stuttgart Office**

Industriestr. 3 70507 Stuttgart, Germany Tel: 0711-99010-0 Fax: 0711-99010-19

#### **Hannover Office**

Königstr. 12 30175 Hannover, Germany Tel: 0511-33402-0 Fax: 0511-33402-34

#### **Benelux Office**

Boschdijk 187a 5612 HB Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### **Scandinavia Office**

P.O. Box 134 18322 Taeby, Sweden Tel: 08-6380820 Fax: 08-6380388

# **NEC Electronics (UK) Limited**

Cygnus House, Sunrise Park Way, Milton Keynes, MK14 6NP, U.K.

Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics (France) S.A.

9, rue Paul Dautier-BP 187 78142 Velizy-Villacoublay Cédex France

Tel: 01-30-67-58-00 Fax: 01-30675899

#### **Madrid Office**

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### NEC Electronics Italiana s.r.l.

Via Fabio Filzi, 25/A, 20124 Milano, Italy Tel: 02-667541 Fax: 02-66754299

#### [Asia & Oceania]

# **NEC Electronics Hong Kong Limited**

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886-9318

Fax: 2886-9022/9044

#### Seoul Branch

10F, ILSONG Bldg., 157-37, Samsung-Dong, Kangnam-Ku Seoul, the Republic of Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Taiwan Ltd.**

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-719-2377 Fax: 02-719-5951

#### **NEC Electronics Singapore Pte. Ltd.**

101 Thomson Road #04-02/05 United Square, Singapore 307591

Tel: 253-8311 Fax: 250-3583

G97. 8

Document No. S12238EJ3V0PF00 (3rd edition) Date Published November 1997 N

© NEC Corporation 1997 Printed in Japan